1968/32 COPY 3

COMMONWEALTH OF AUSTRALIA

# DEPARTMENT OF NATIONAL DEVELOPMENT

BUREAU OF MINERAL RESOURCES, GEOLOGY AND GEOPHYSICS

RECORD No. 1968 / 32

# Crystal Timing Unit Type NCD 2

by

M.S. JONES

The information contained in this report has been obtained by the Department of National Development as part of the policy of the Commonwealth Government to assist in the exploration and development of mineral resources. It may not be published in any form or used in a company prospectus or statement without the permission in writing of the Director, Bureau of Mineral Resources, Geology & Geophysics.

# RECORD No. 1968 / 32

# Crystal Timing Unit Type NCD 2

by

M.S. JONES

The information contained in this report has been obtained by the Department of National Development as port of the policy of the Commonwealth Government to assist in the exploration and development of mineral resources. It may not be published in any form or use in a company prospectus or statement without the permission in writing of the Director, Bureau of Mineral Resources, Geology and Geophysics.

# CONTENTS

|     | SUMMAR                                  | YY                                               | Page     |

|-----|-----------------------------------------|--------------------------------------------------|----------|

| 1.  | SPECIF                                  | TICATIONS                                        | 1        |

| 2.  | GENERAL DESCRIPTION                     |                                                  |          |

|     | 2,1,                                    | Introduction                                     | § ±      |

|     | 2.2.                                    | Functions                                        | 2        |

| .00 | 2.3.                                    | System Concept                                   | 3        |

| 3.  | CIRCUIT DESCRIPTIONS                    |                                                  |          |

|     | 3.1.                                    | Crystal Oscillator Unit O1                       | 5<br>5 1 |

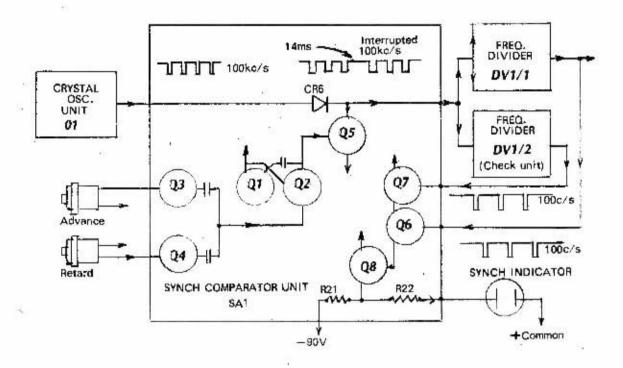

|     | 3.2.                                    | Synchronisation Comparator Unit SA1              | 6        |

|     | 3.3.                                    | Decade Frequency Divider Units DV1/1 and DV1/2   | 10       |

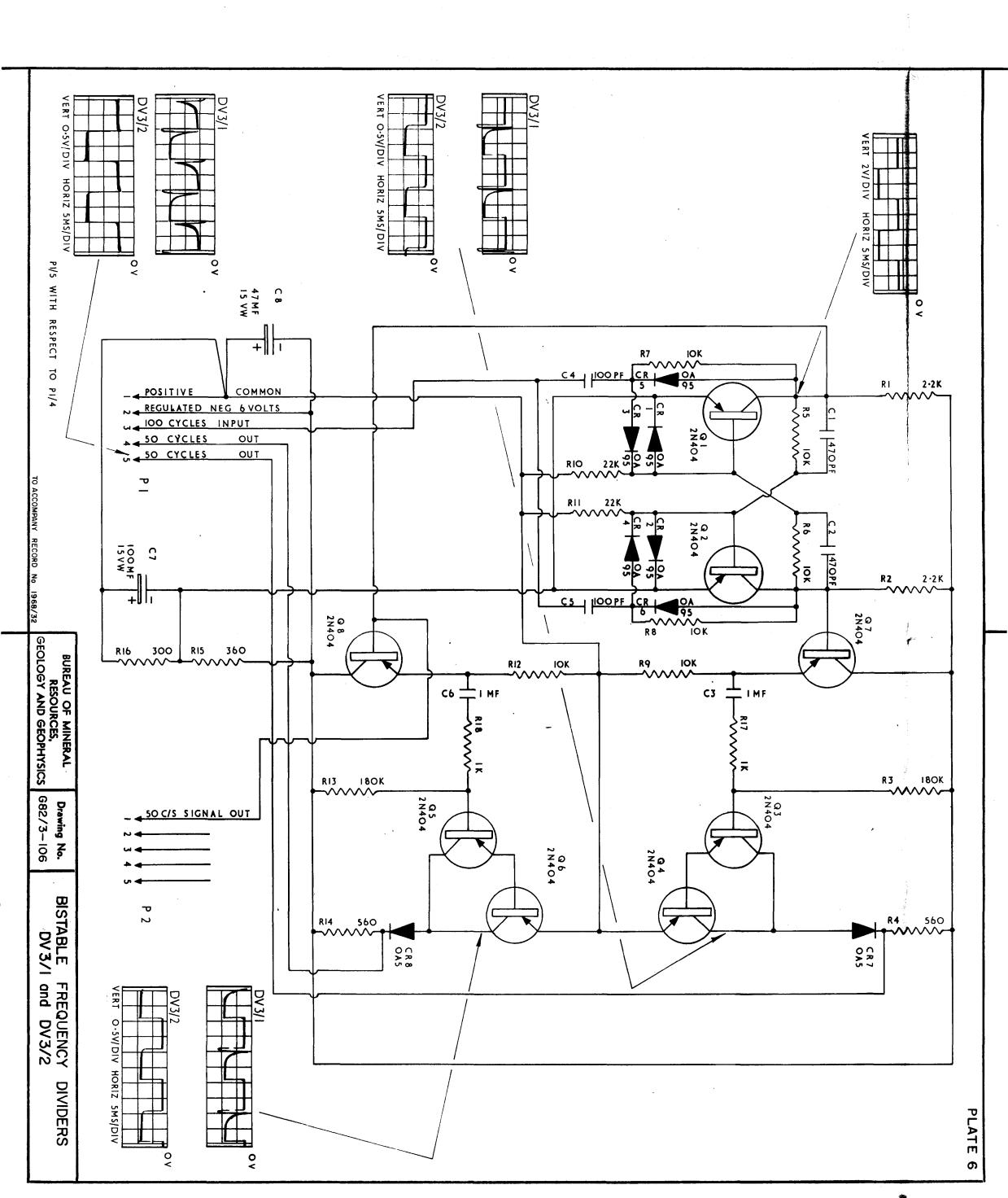

|     | 3.4.                                    | Bistable Frequency Divider Units DV3/1 and DV3/2 | 11       |

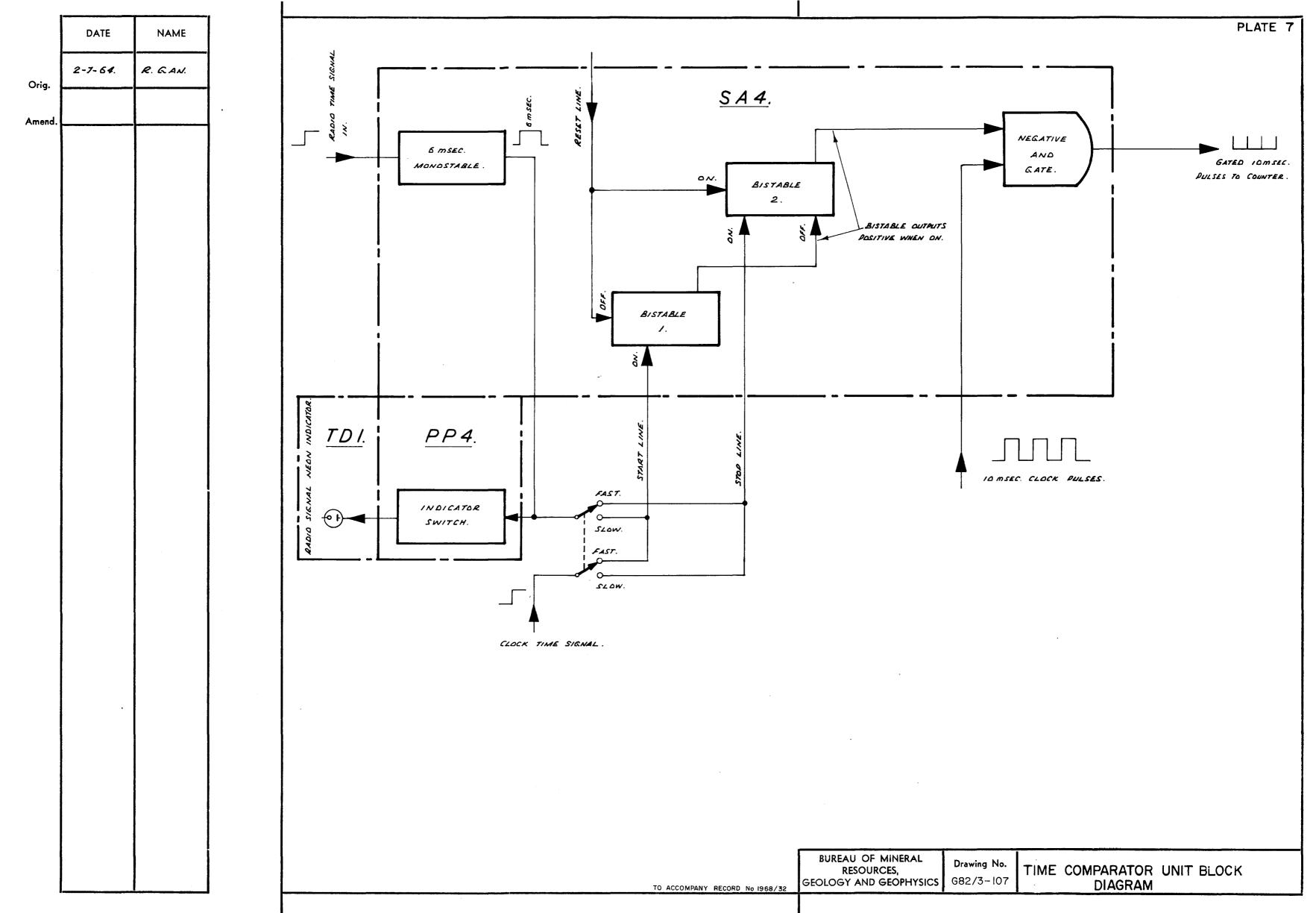

|     | 3.5.                                    | Time Comparator Unit SA4                         | 12       |

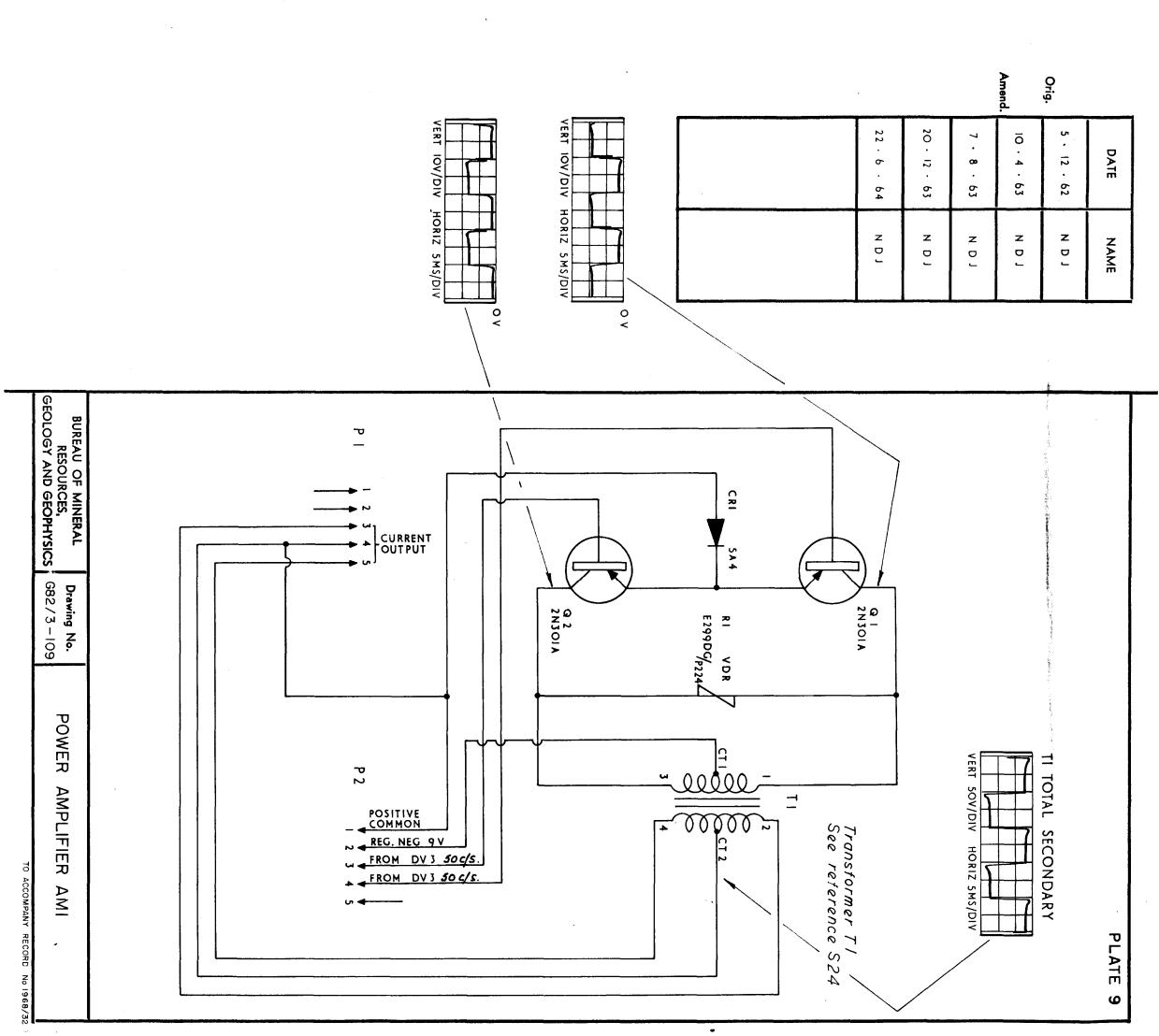

|     | 3.6.                                    | Power Amplifier Units AM1, AM2, and AM3          | 13       |

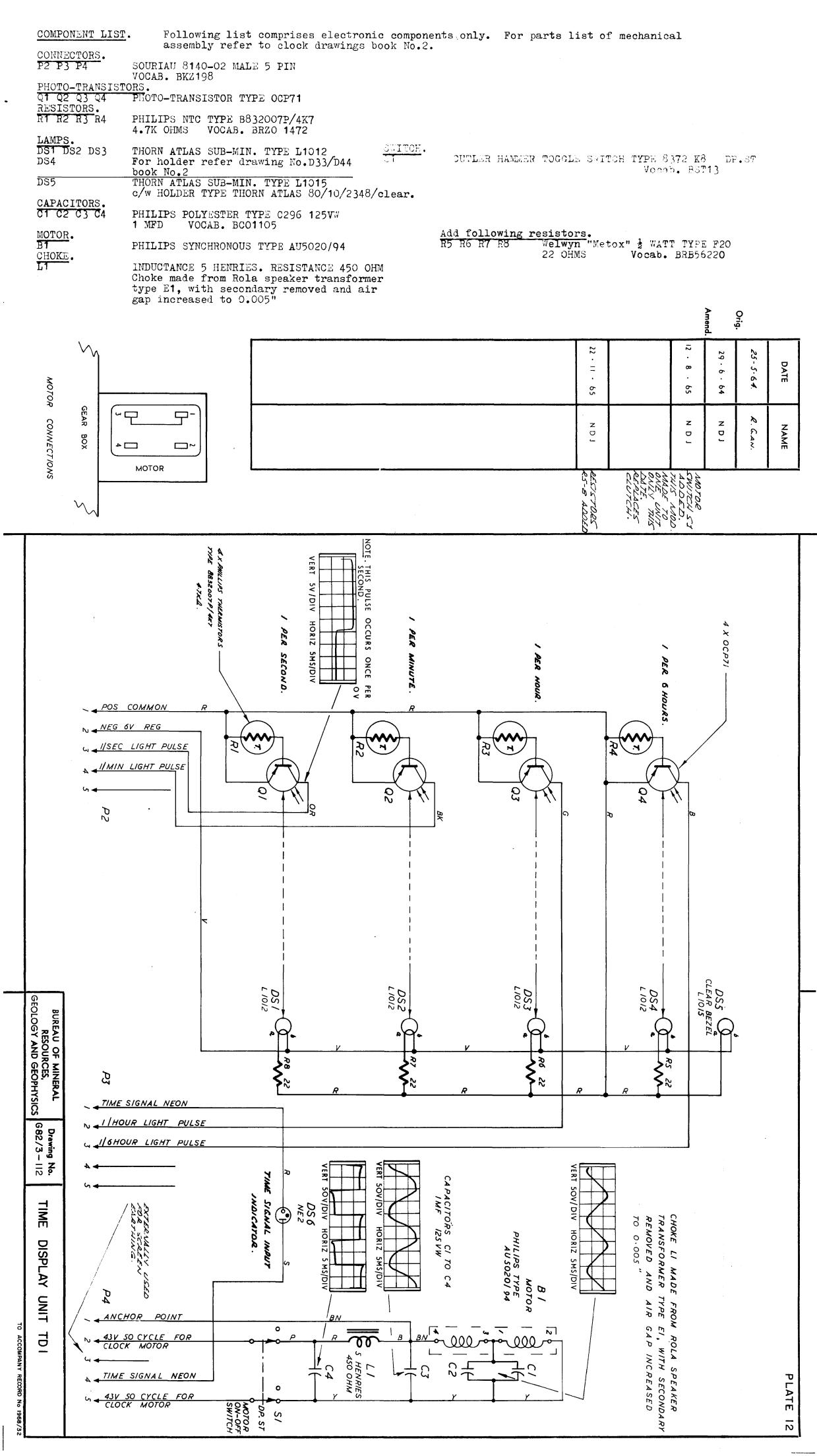

|     | 3.7.                                    | Time Display Unit and Light-gate Generator TD1   | 14       |

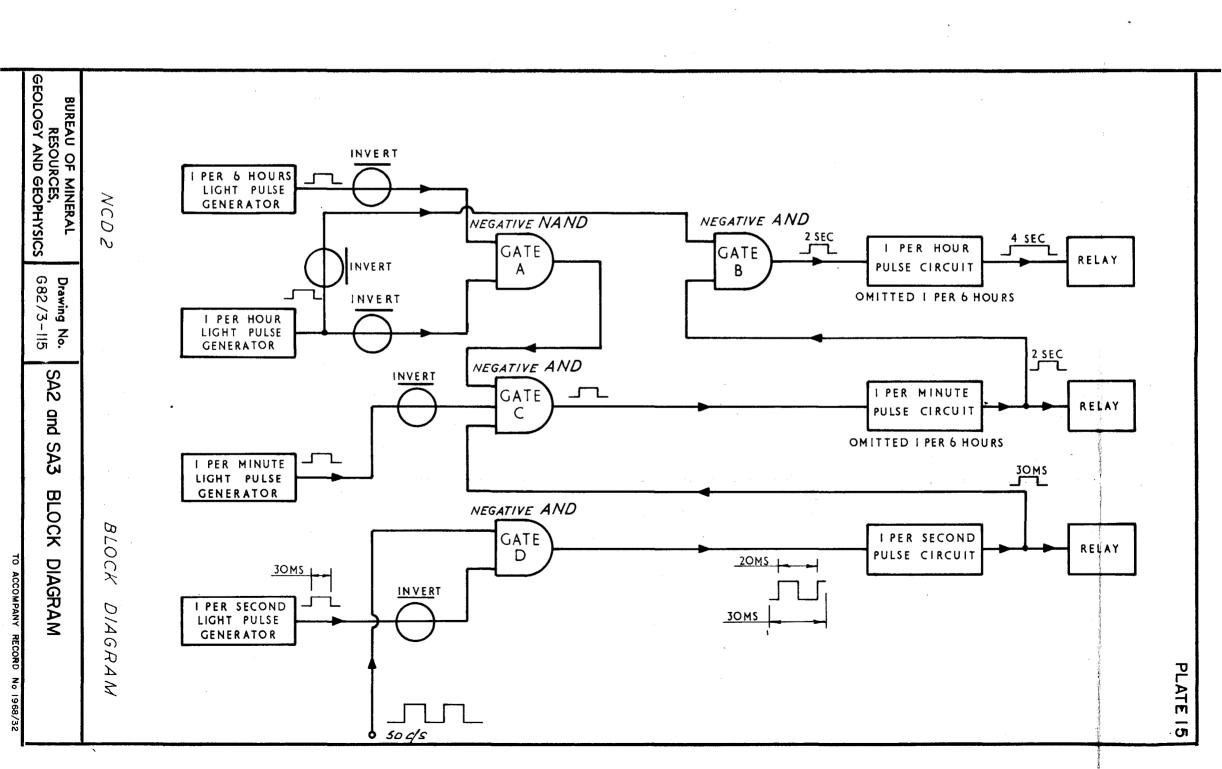

|     | 3.8.                                    | Light-gate and Monostable circuits and           | 1.:      |

|     |                                         | timing relays, SA2 and SA3                       | 15       |

|     | 3.9.                                    | Decade Frequency Divider and Readout Meter Units | 18       |

|     |                                         | DV2/1 and DV2/2                                  |          |

|     | 3.10:                                   | -6 Volt and -9 Volt Regulated Power Supply Units | -19      |

|     |                                         | PP1 and PP2                                      | 100      |

|     | 3.11.                                   | -10 Volt Regulated Power Supply Unit PP3         | 21       |

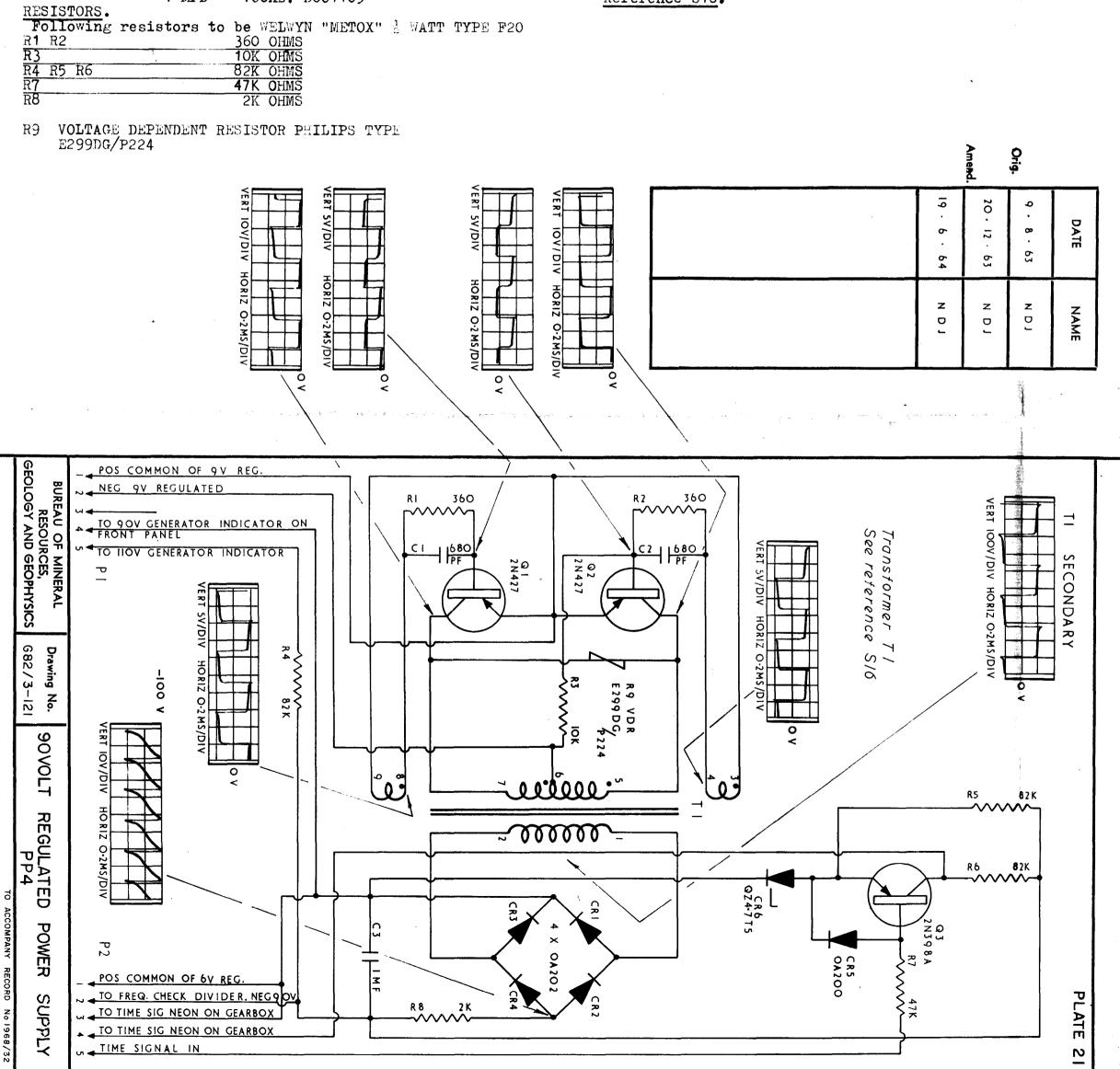

|     | 3.12.                                   | -90 Volt Regulated Generator PP4                 | 21       |

| 4.  | INSTALLATION AND OPERATING INSTRUCTIONS |                                                  |          |

|     | 4.1.                                    | Preliminary checks                               | 23       |

|     | 4.2.                                    | Grand connection                                 | 23       |

|     | 4.3.                                    | Connections to front panel                       | 23       |

|     | 4.4.                                    | Switching on                                     | 24       |

|     | 4.5.                                    | Checking the voltage regulator adjustments       | 25       |

|     | 4.6.                                    | Checking time-mark operations                    | 25       |

|     | 4.7.                                    | Checking readout meters                          | 27       |

|     | 4.8.                                    | Function of the FAST-SLOW switch                 | 28       |

|     | 4.9.                                    | Setting the Time Display to correct time         | 28       |

|     | 4:10.                                   | Adjusting the clock rate                         | 29       |

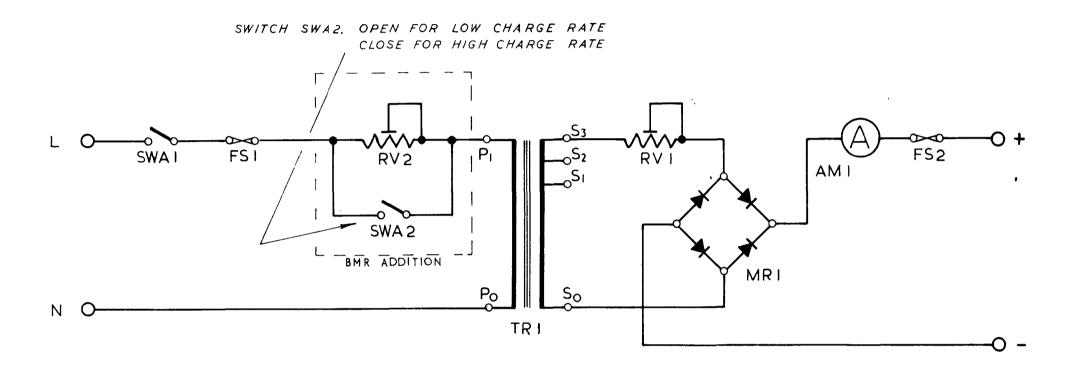

|     | 4.11,                                   | Adjusting the charge rate of the battery charger | 30       |

|     | 4.12.                                   | Brake tension                                    | 30       |

|     | 4.13.                                   | Routine checks during operation                  | 30       |

|                                                      | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5. MAINTERANCE                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.1. General                                         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.2. Fault-finding                                   | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

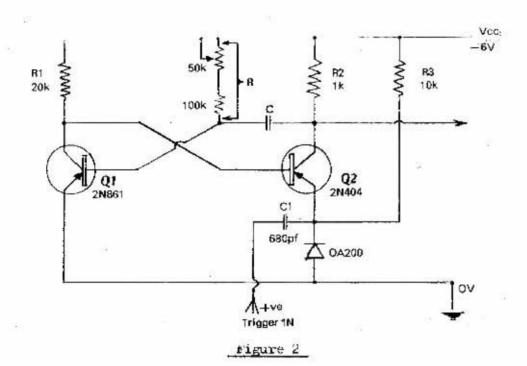

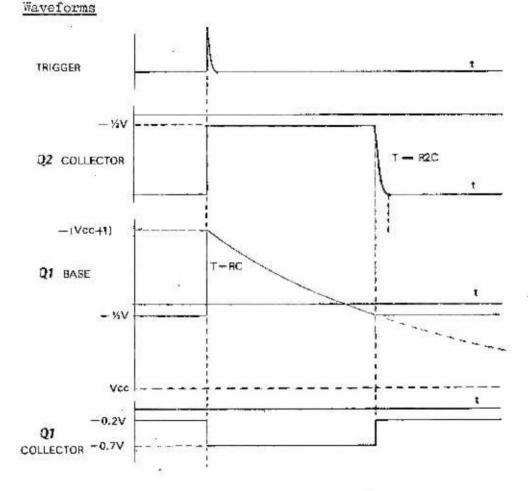

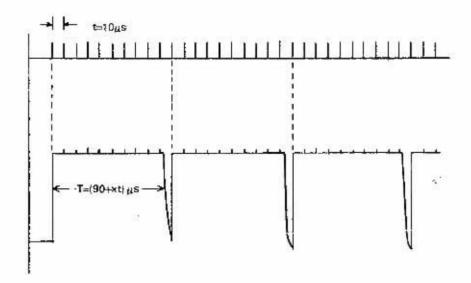

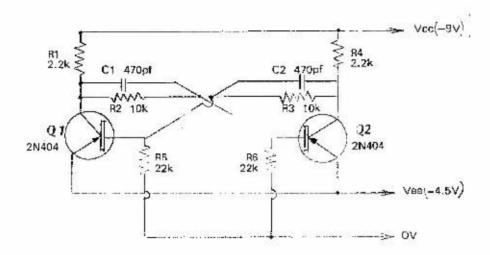

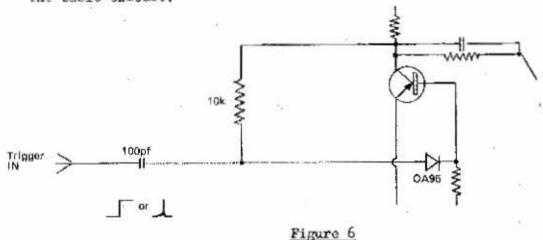

| APPENDIX 1. The Cooke-Yarborough monostable multiv   | ibrator 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

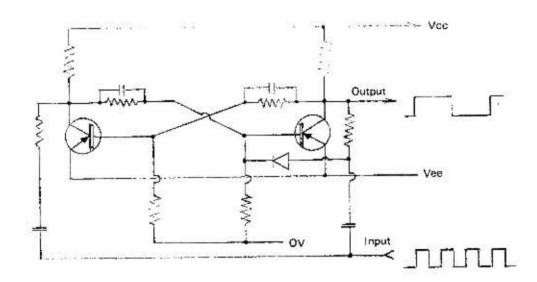

| APPENDIX 2. The bistable multivierator               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| APPENDIX 3. Gating circuits used in the ICD2         | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ILLUSTRATIONS                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

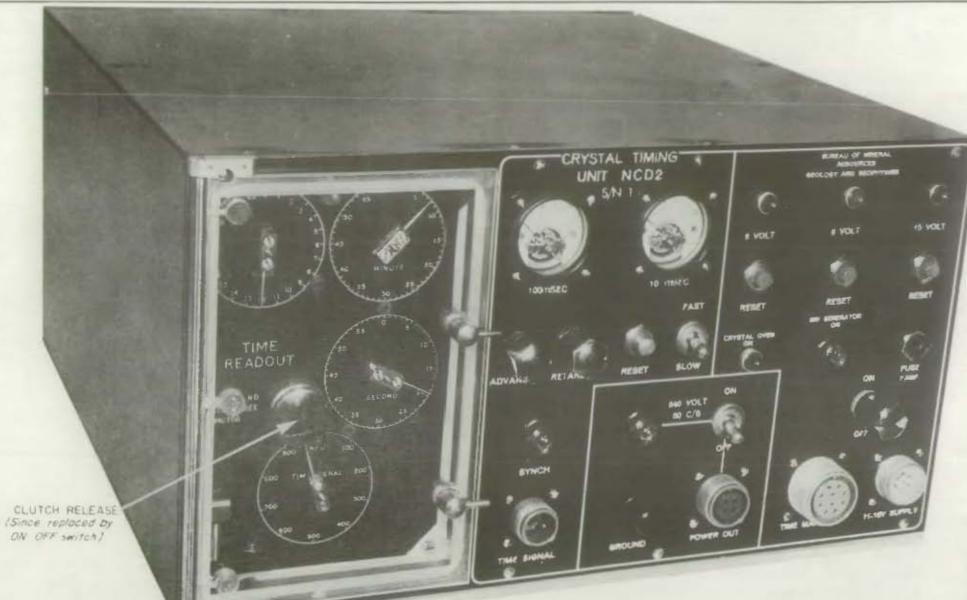

| Plate 1. Crystal Timing Unit NCD2 (                  | Drawing No. G82/3-101)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

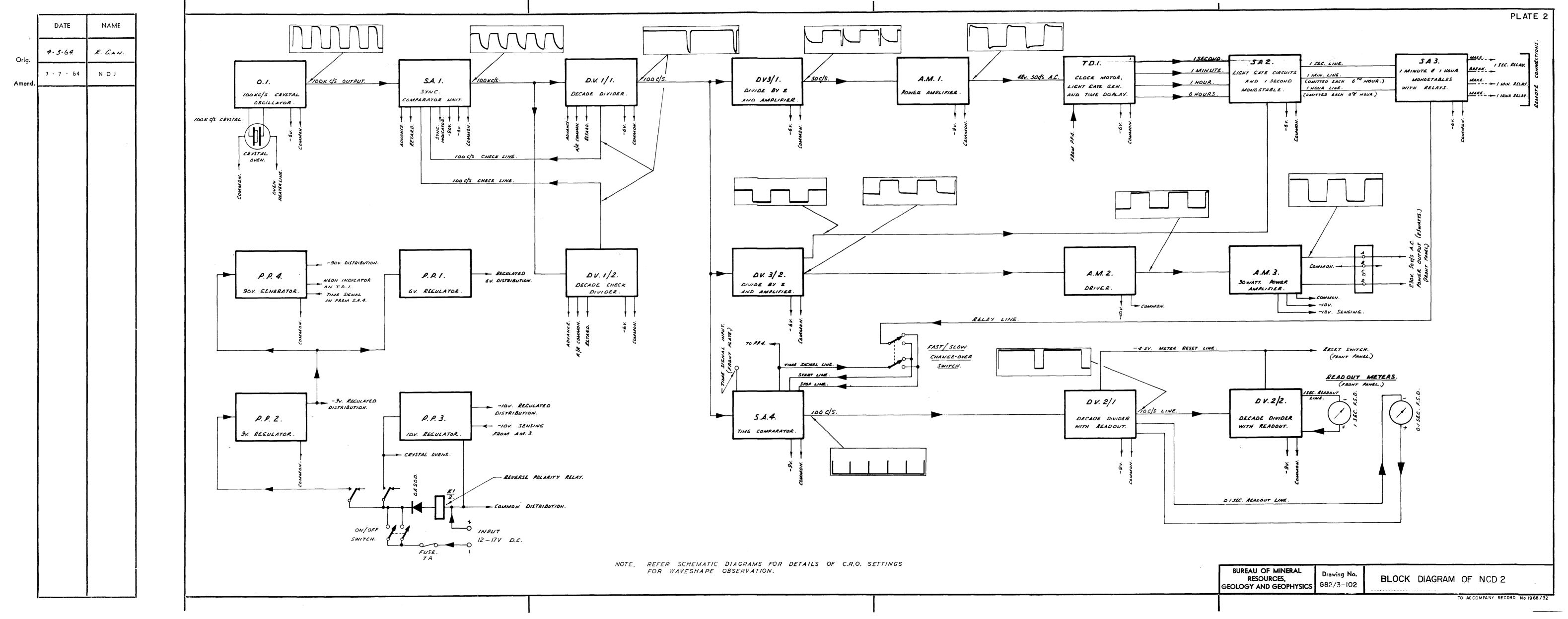

| Plate 2. Block diagram of NCD2                       | (G82/3-102)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

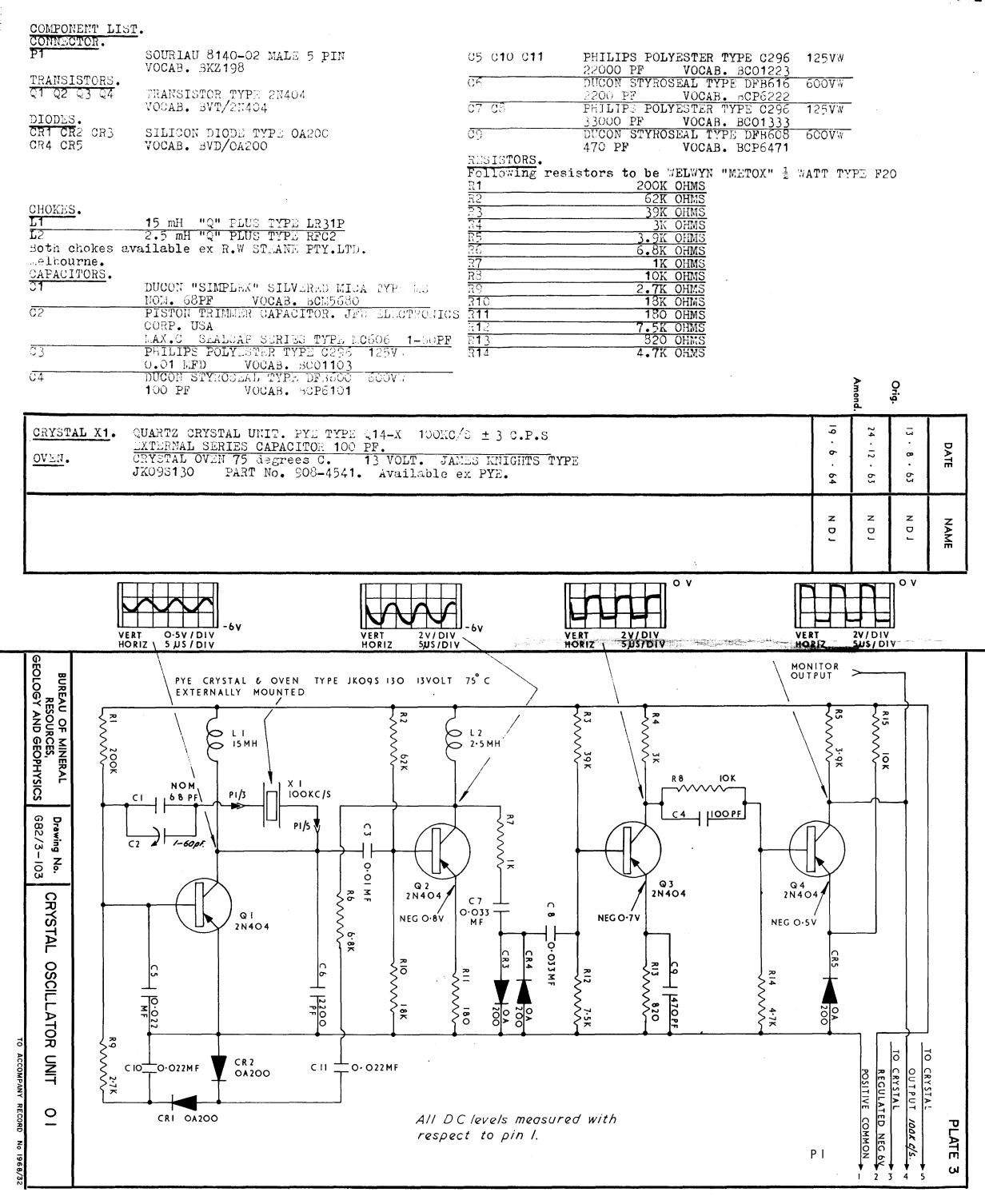

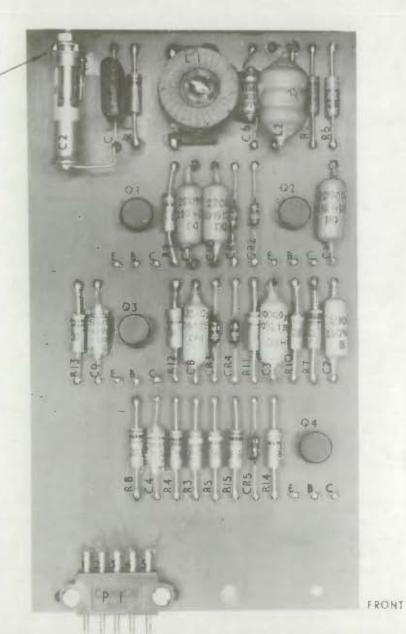

| Plate 3. Crystal oscillator unit 01                  | (G82/3-103)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

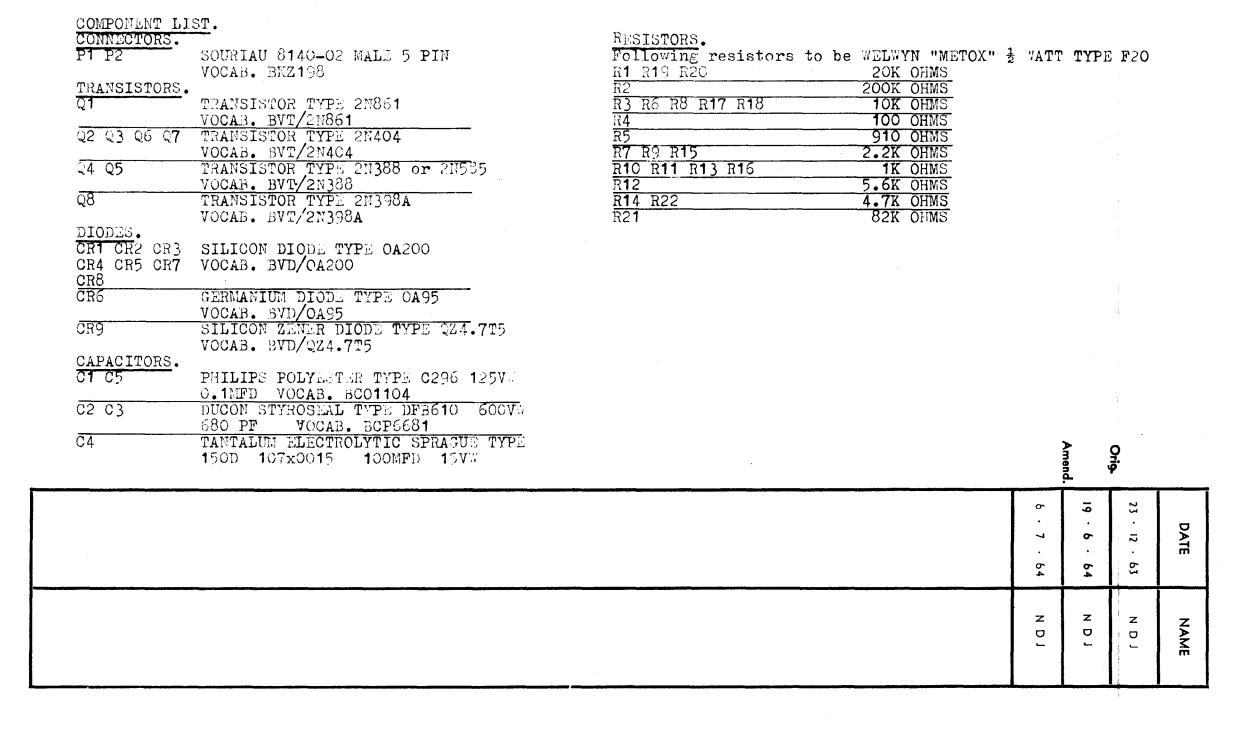

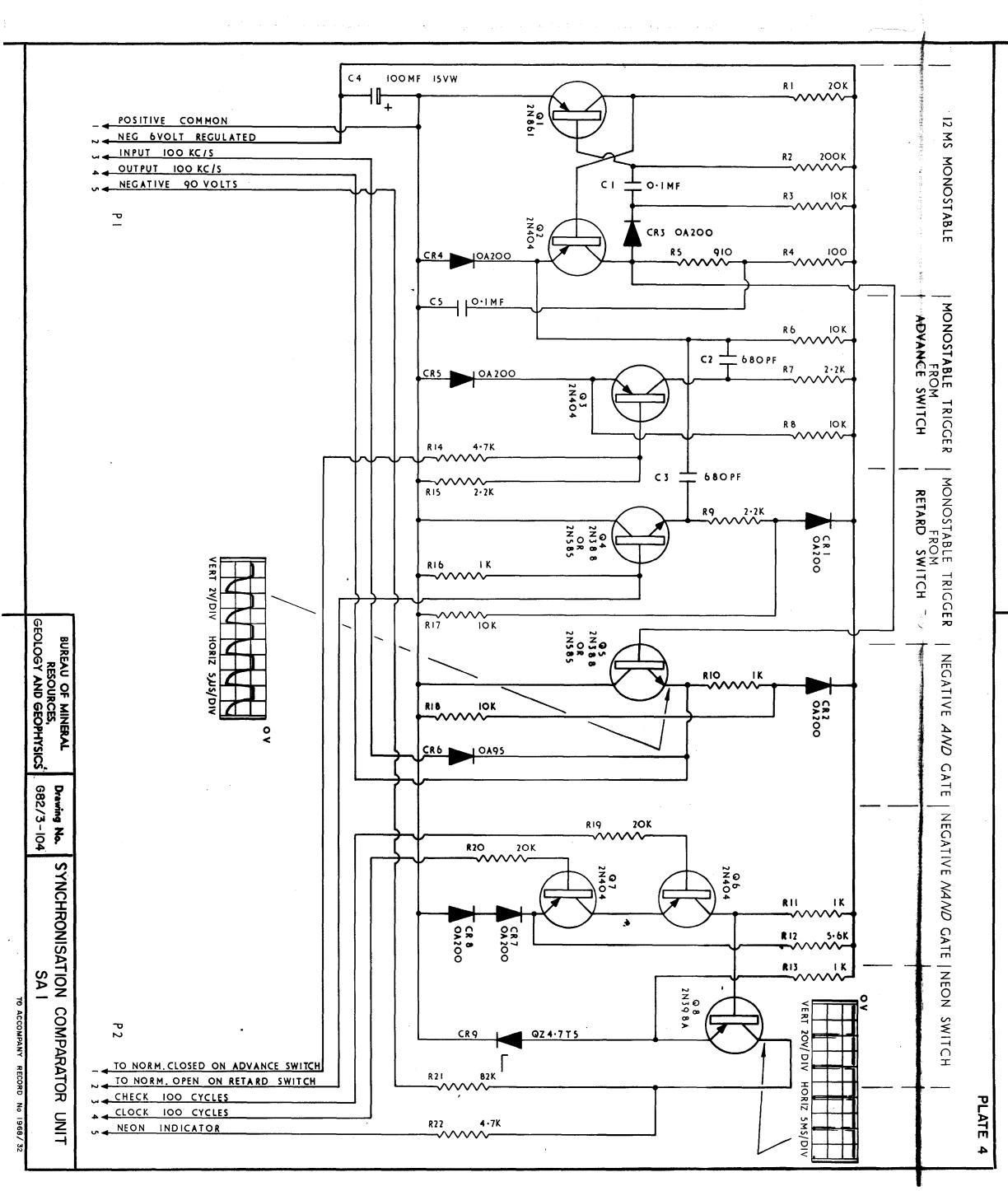

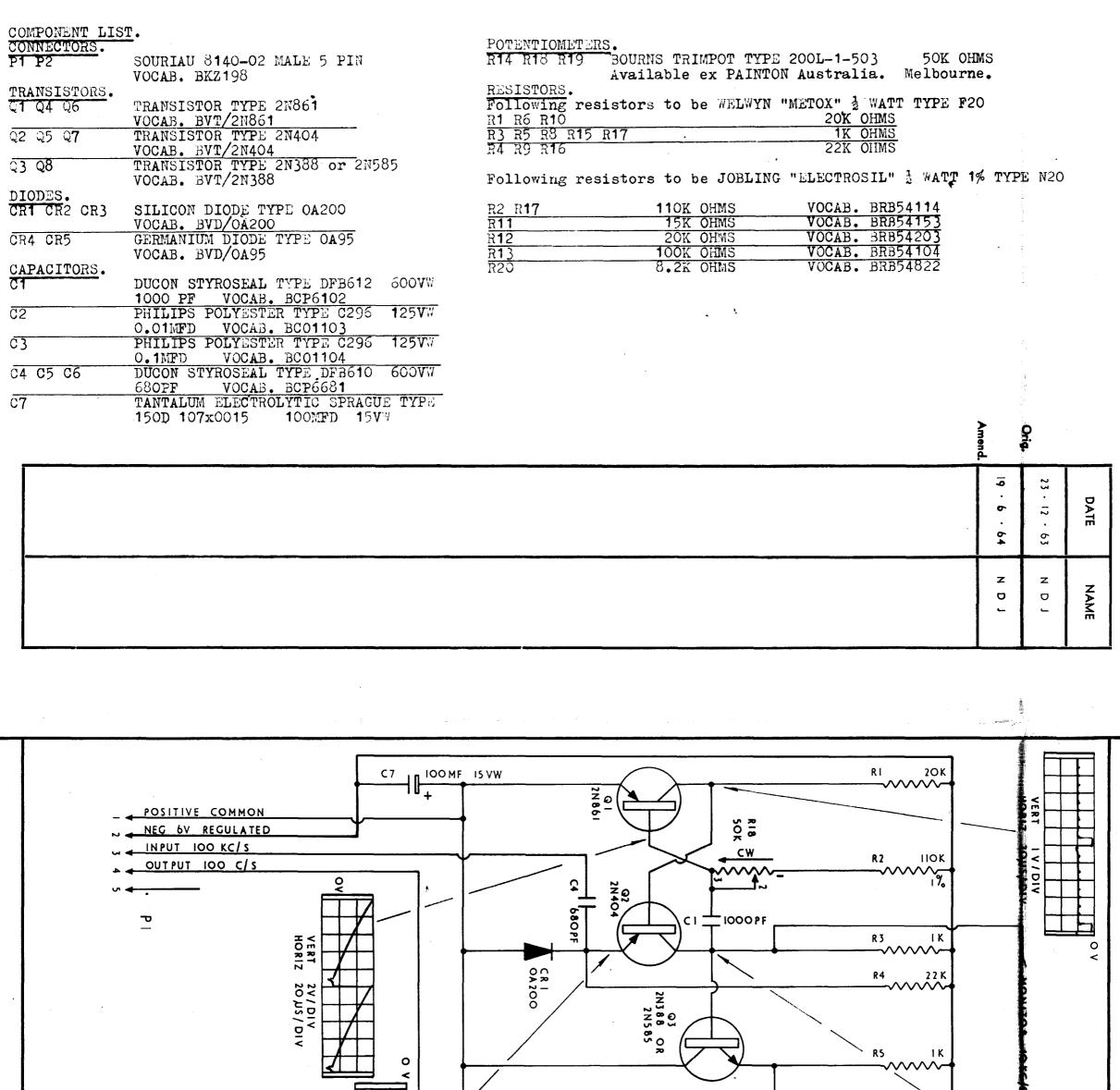

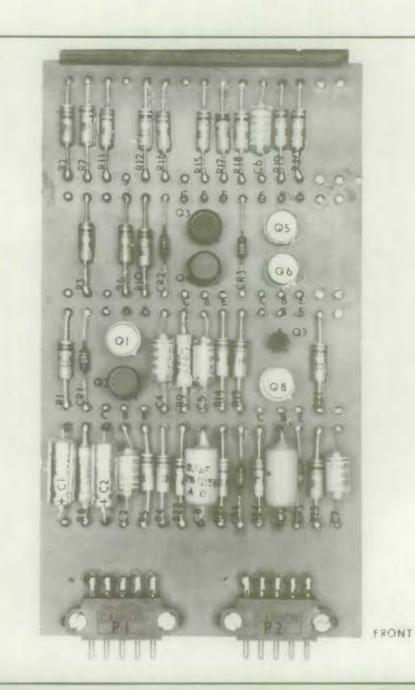

| Plate 4. Synchronisation comparator unit SA1         | (G82/3-104)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

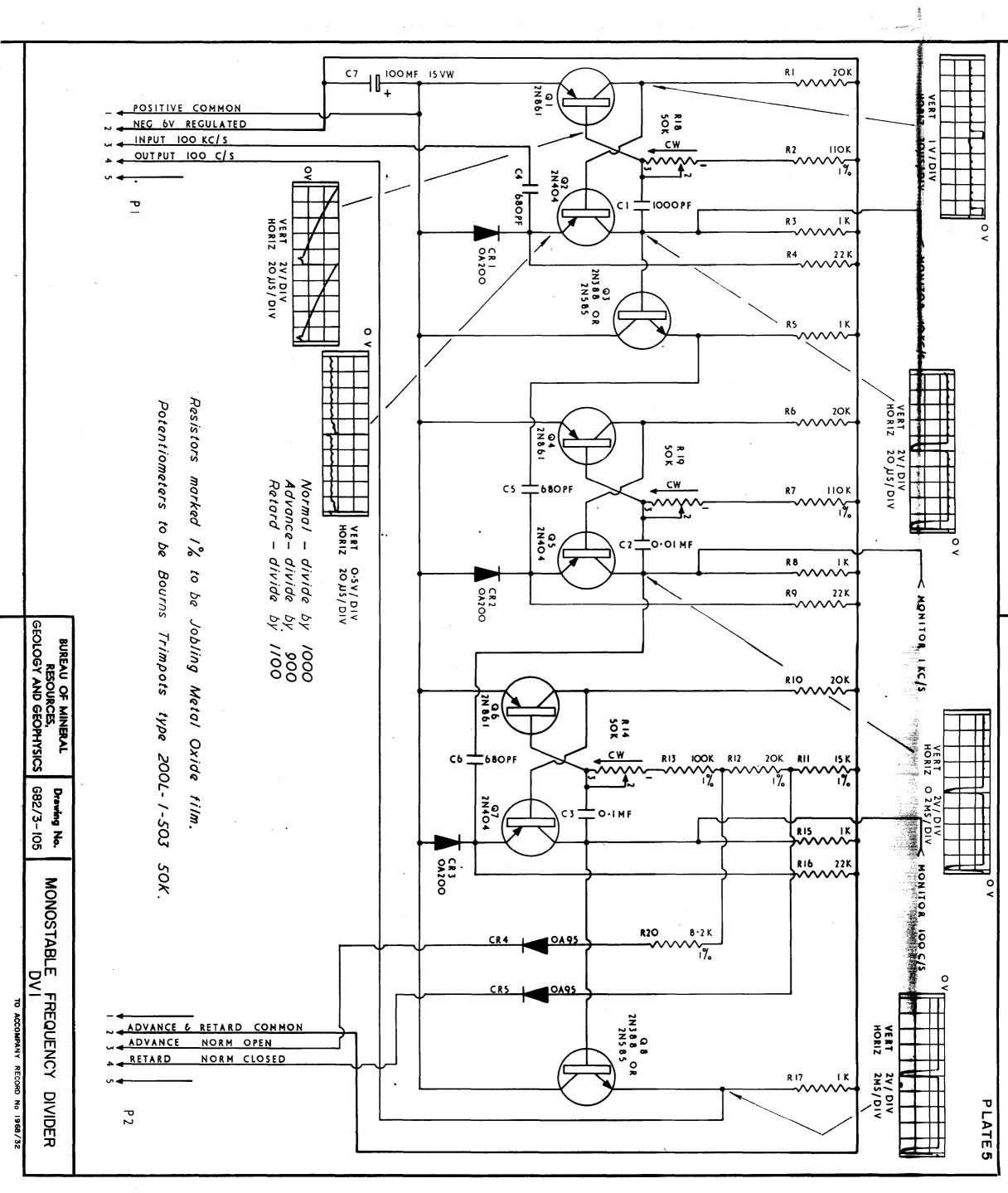

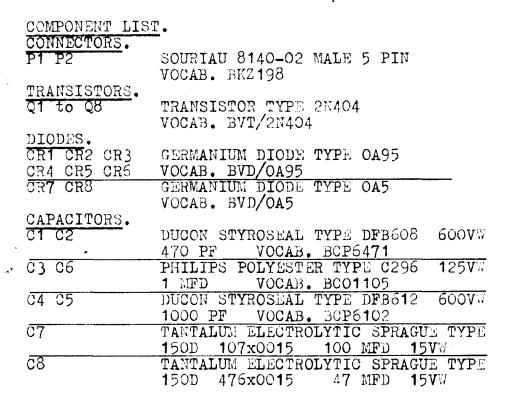

| Plate 5. Monostable frequency divider DV1            | (G82/3-105)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 6. Bistable frequency dividers DV3/1 and DV3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Plate 7. Time comparator unit block diagram          | (G82/3-107)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 8. Time comparator unit SA4                    | (682/3-108)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 9. Power amplifier AM1                         | (G82/3-109)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 10. Power amplifier AM2                        | (G82/3-110)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 11. Power amplifier AM3                        | (G82/3-111)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 12. Time display unit TD1                      | (G82/3-112)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

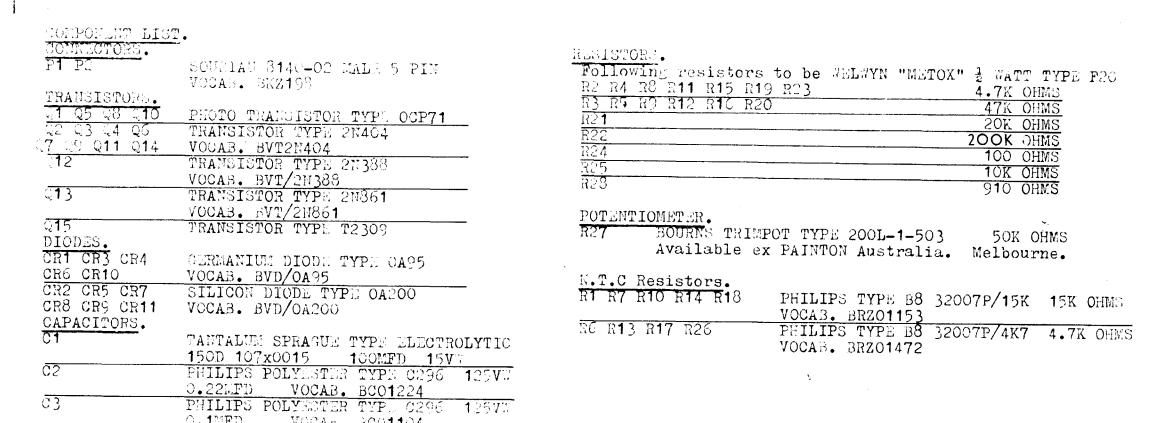

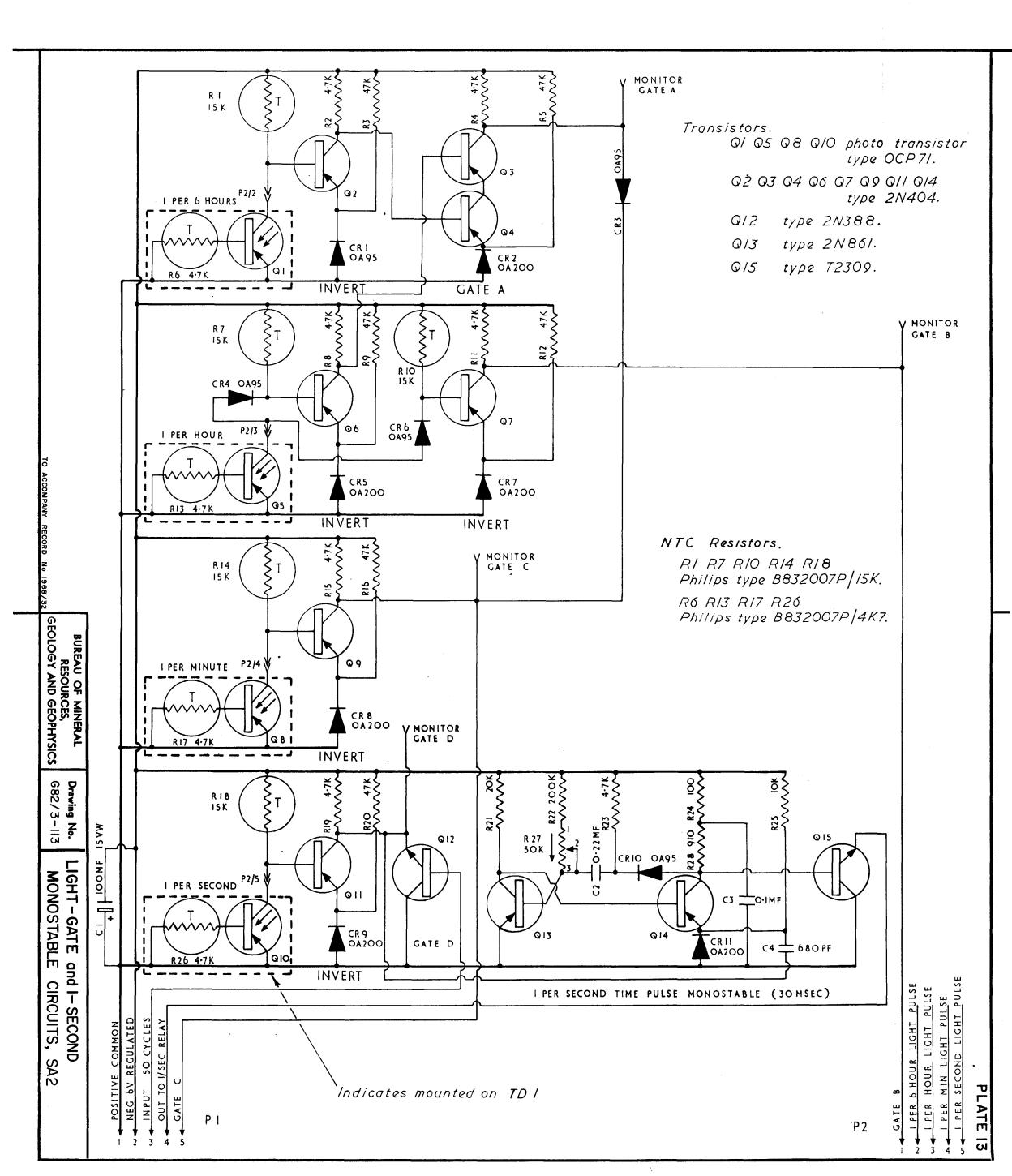

| Plate 13. Light-gate and 1-second monostable circui- | ts, SA2 (G82/3-113)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

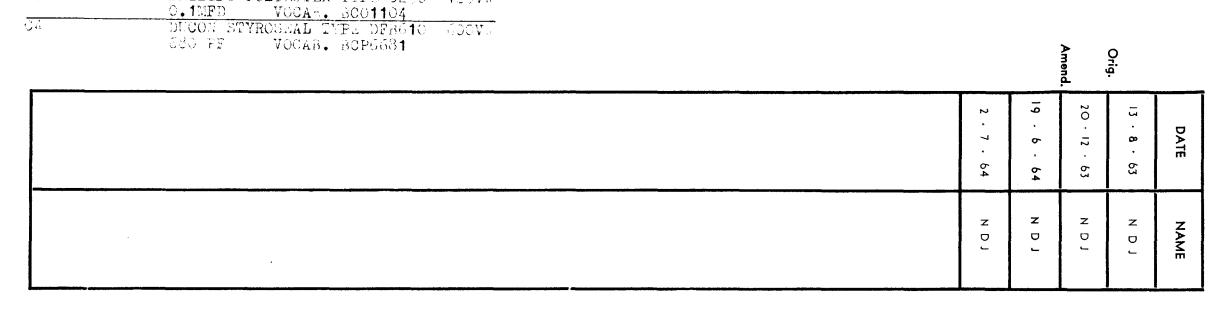

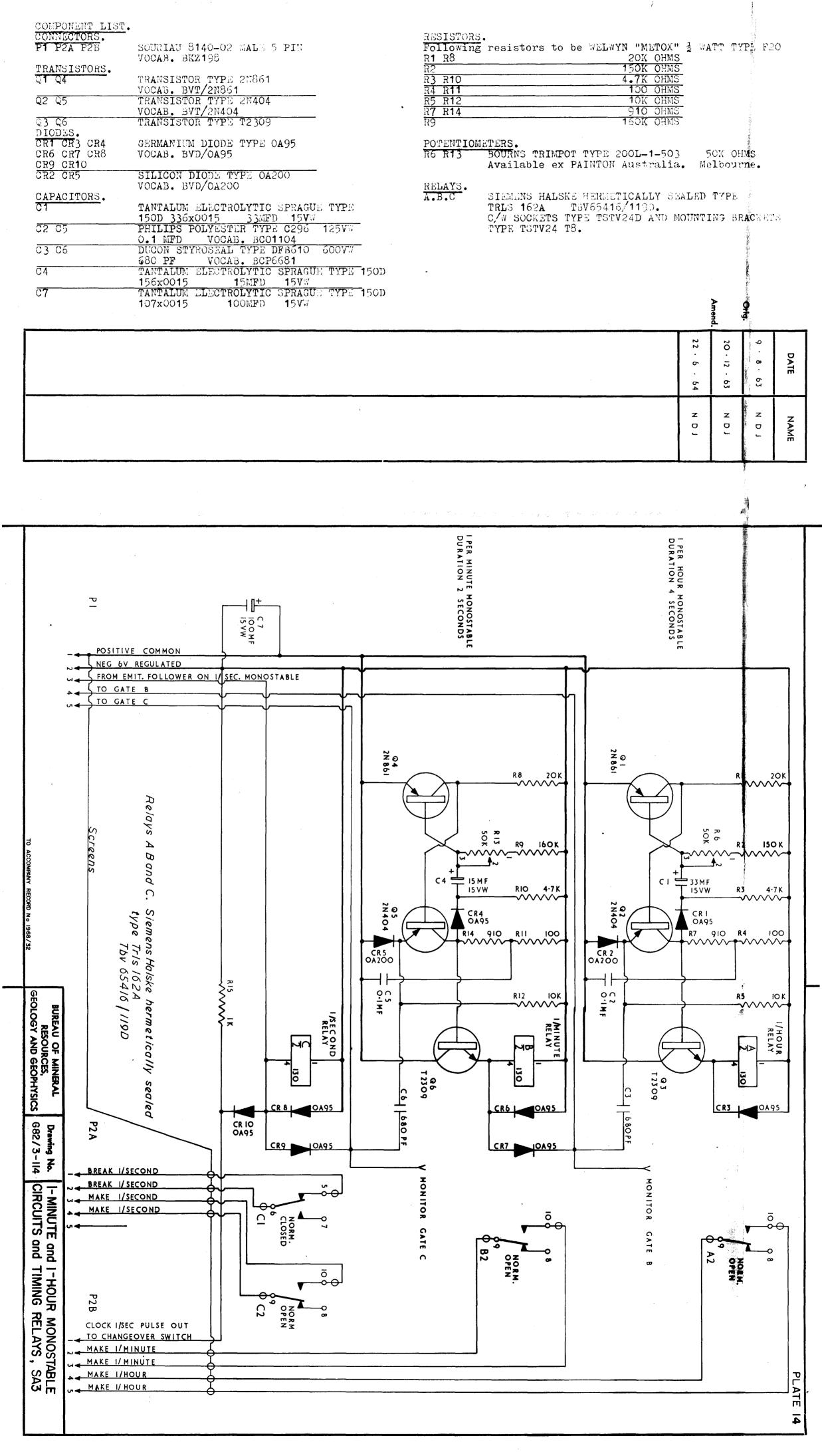

| Plate 14. 1-minute and 1-hour monostable circuits a  | nd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| timing relays, SA3                                   | (G82/3-114)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 15. SA2 and SA3 block diagram                  | (G82/3-115)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 16. Decade frequency dividers JW2              | (G82/3-116)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

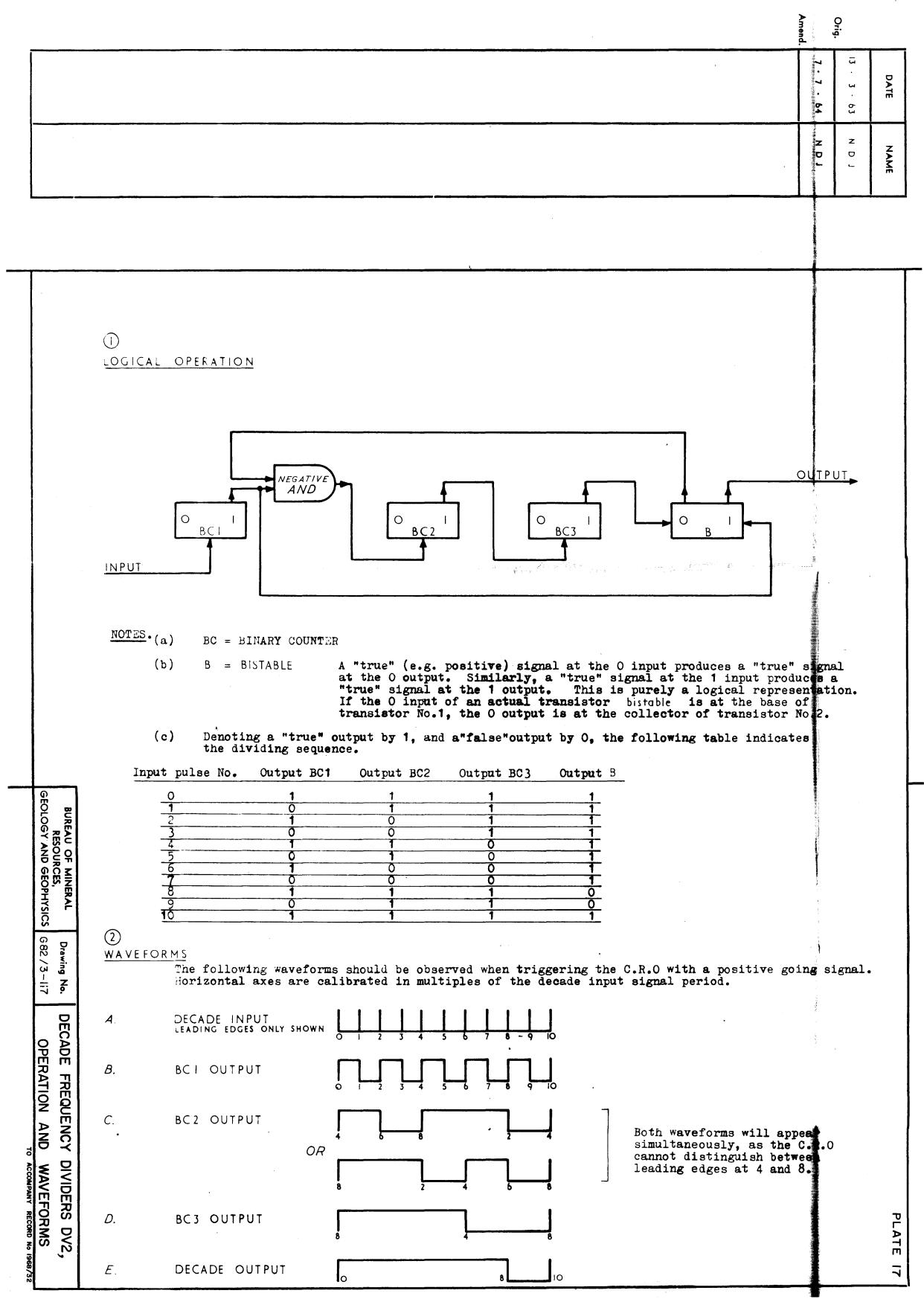

| Plate 17. Decade frequency dividers DV2, operation   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| and waveforms                                        | (G82/3-117)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

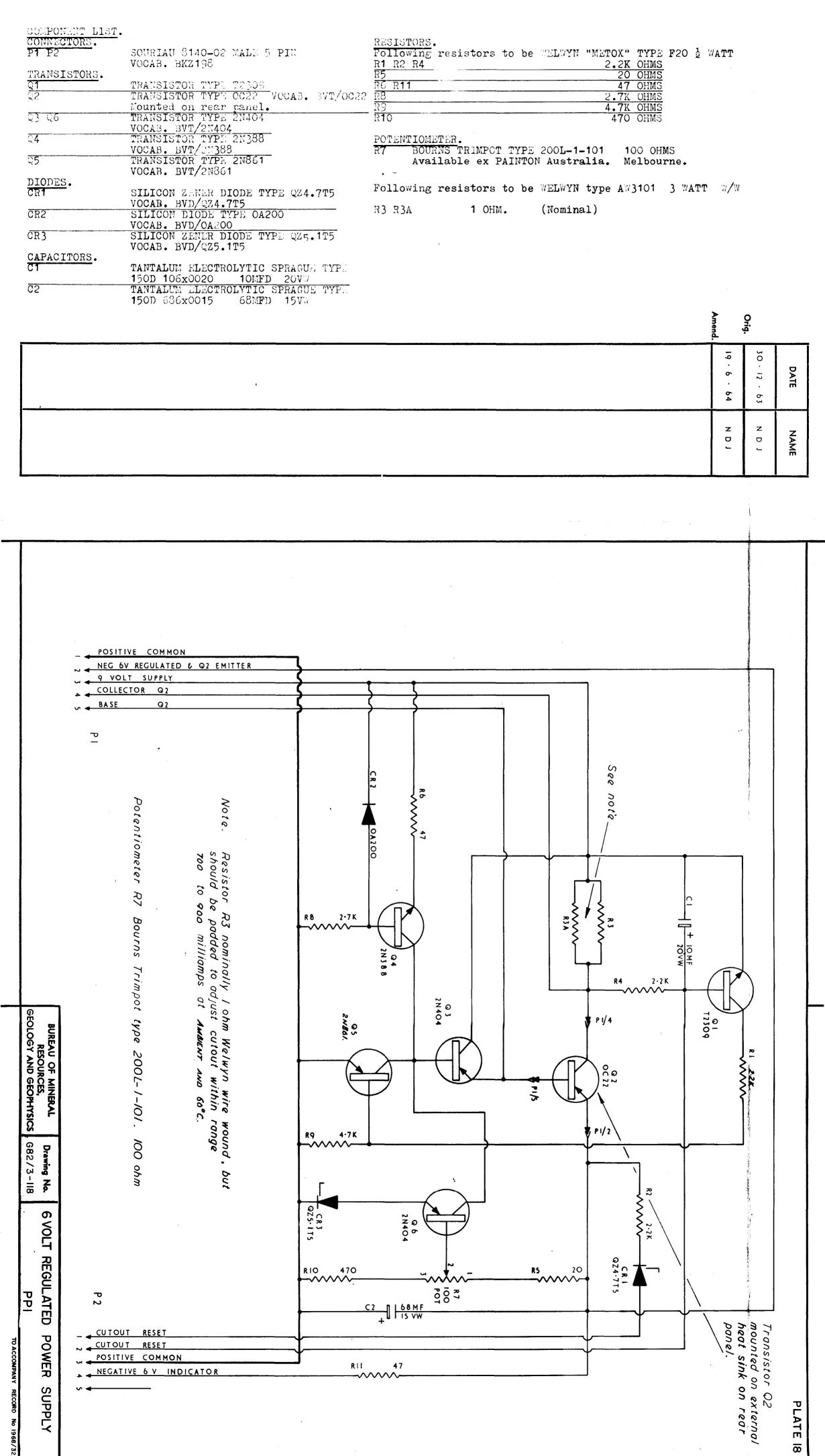

| Plate 186 volt regulated power supply PP1            | (G82/3-118)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

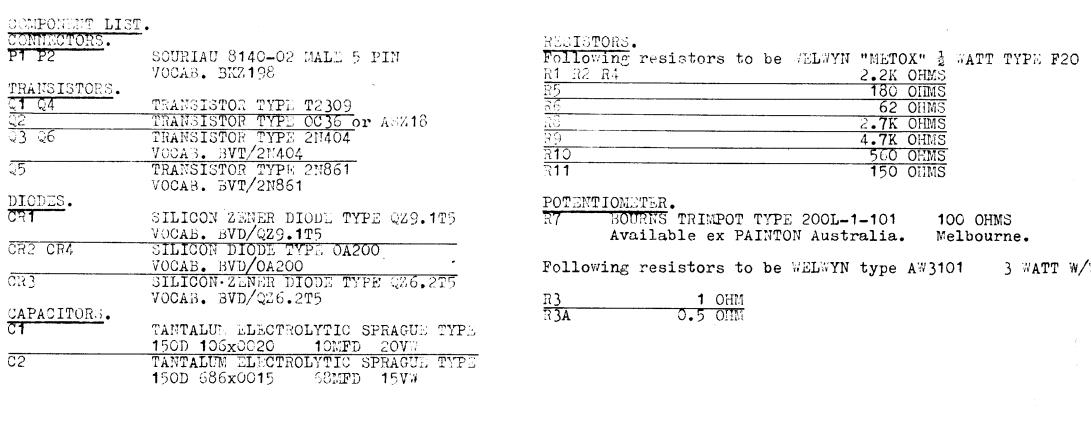

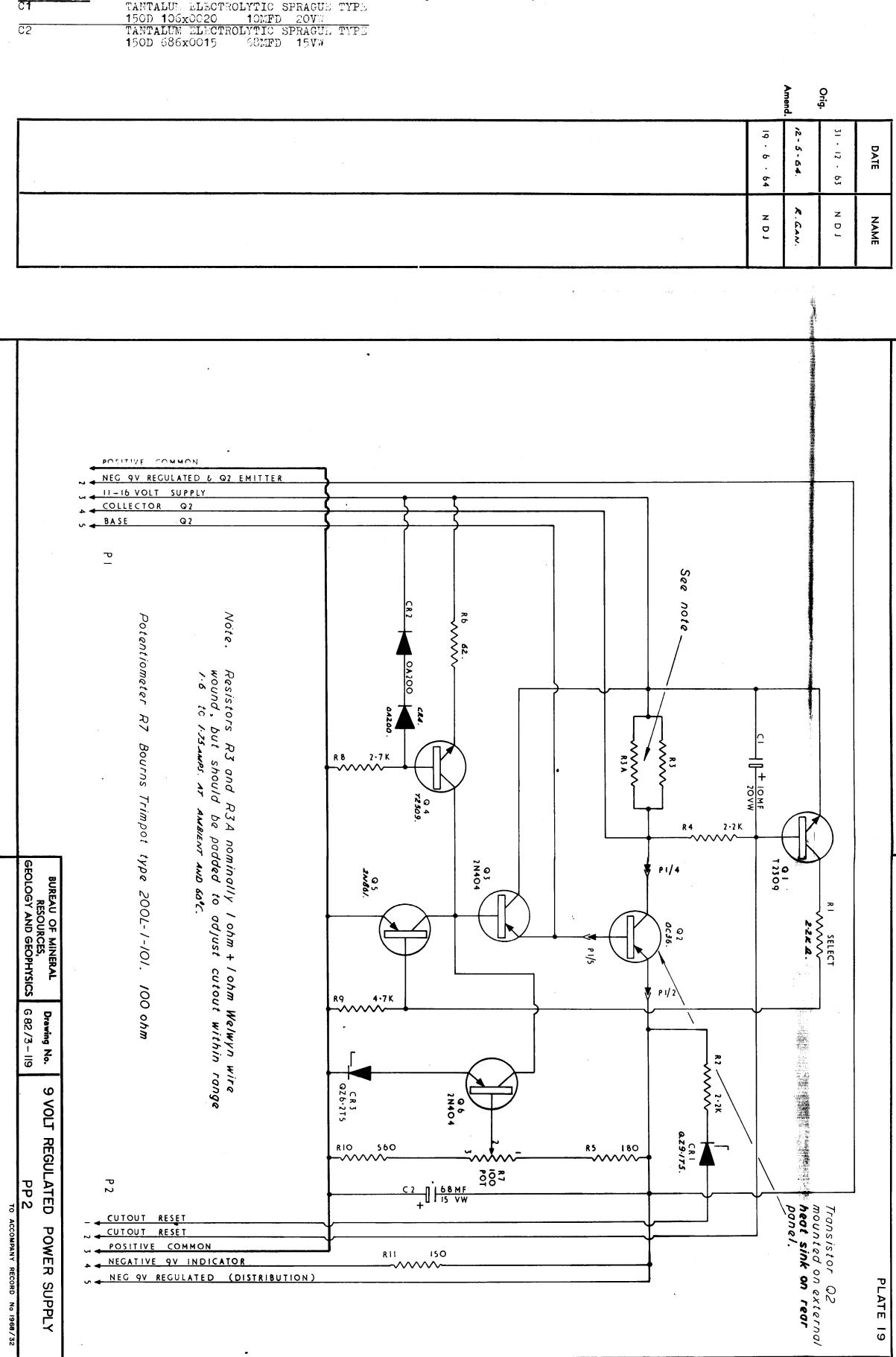

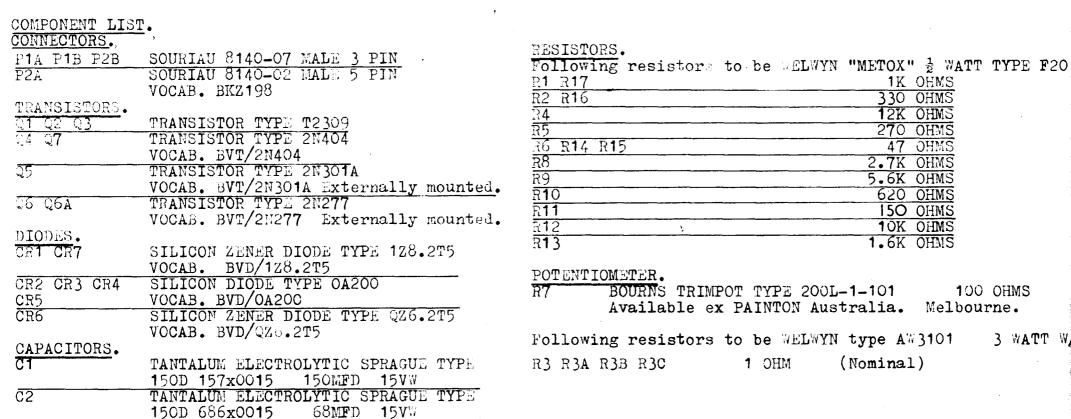

| Plate 199 volt regulated power supply PP2            | (G82/3-119)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

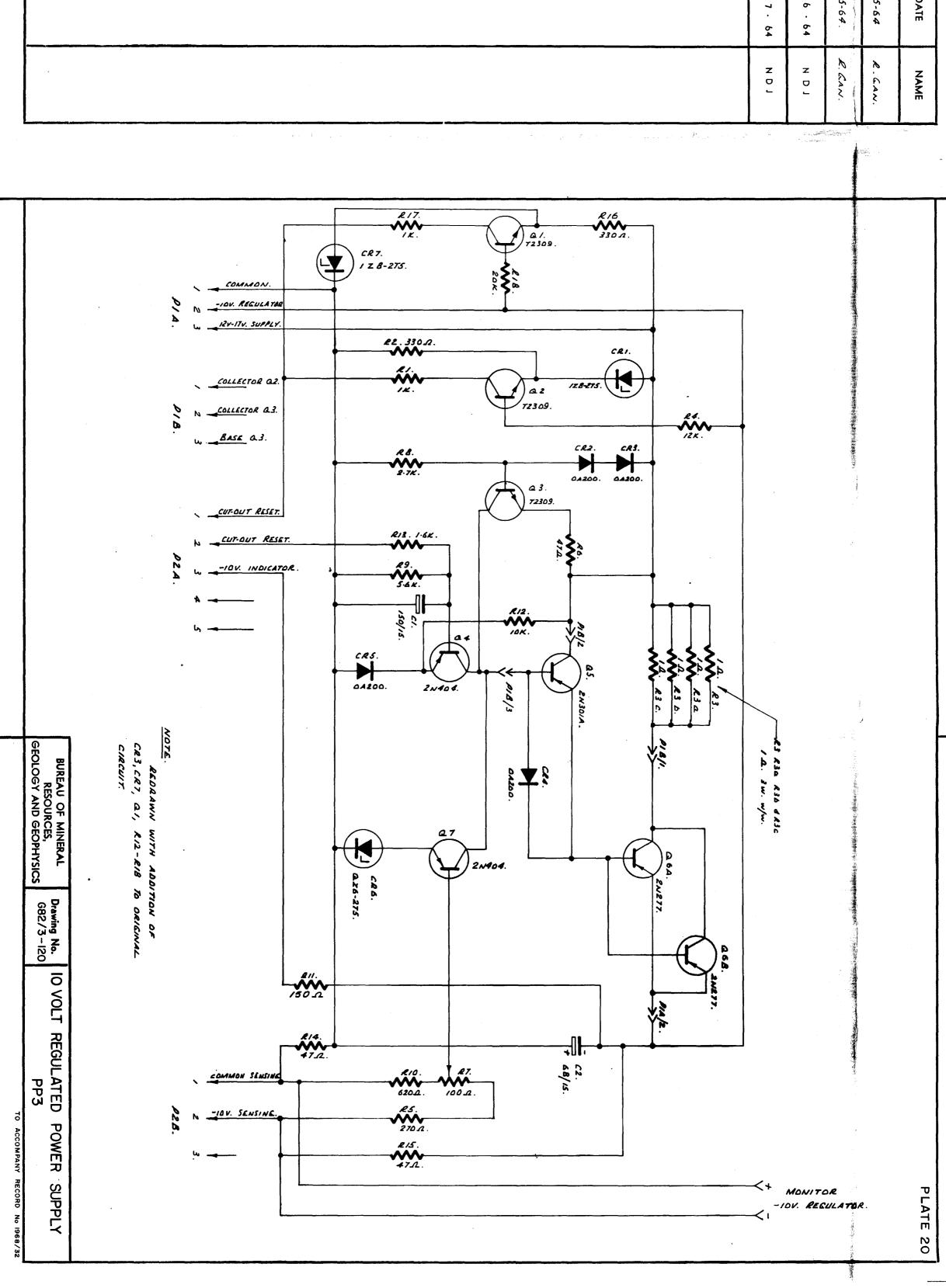

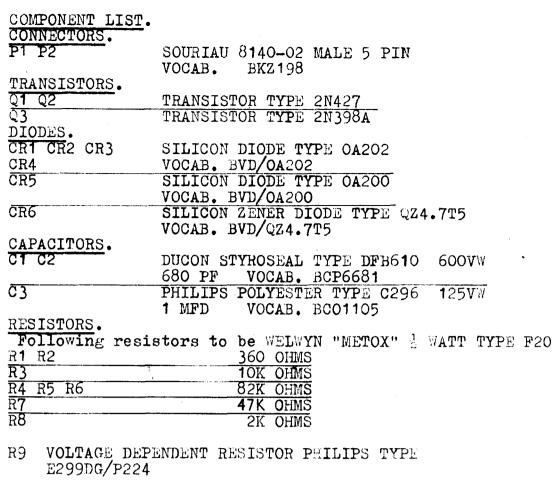

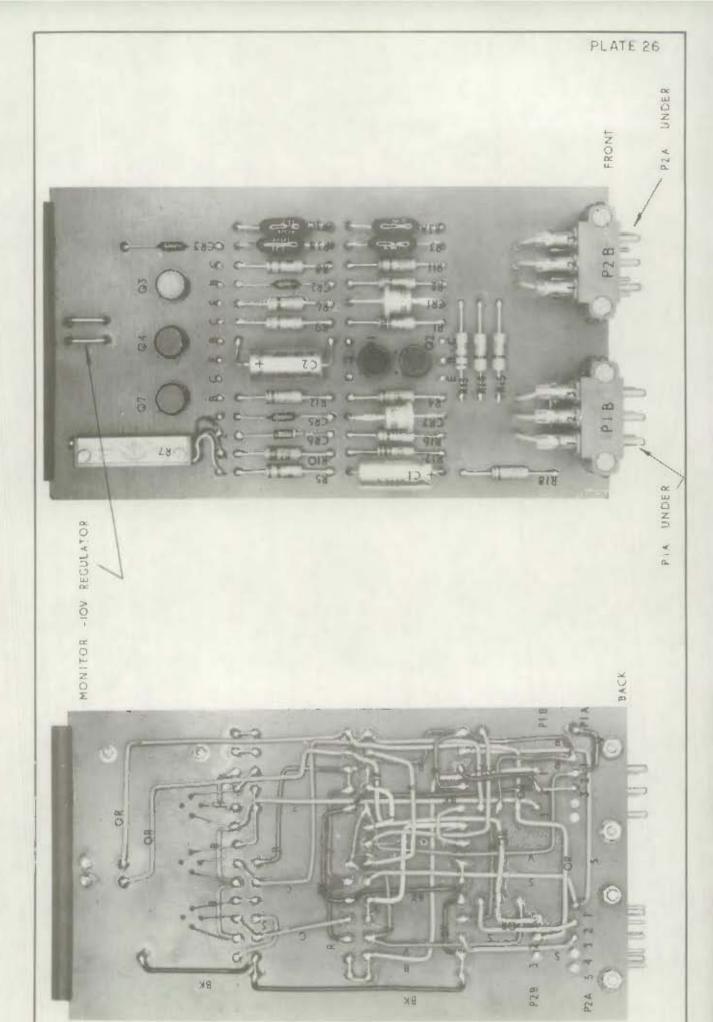

| Plate 2010 volt regulated power supply PP3           | (G82/3-120)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Plate 2190 volt regulated power supply FP4           | (G82/3-121)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

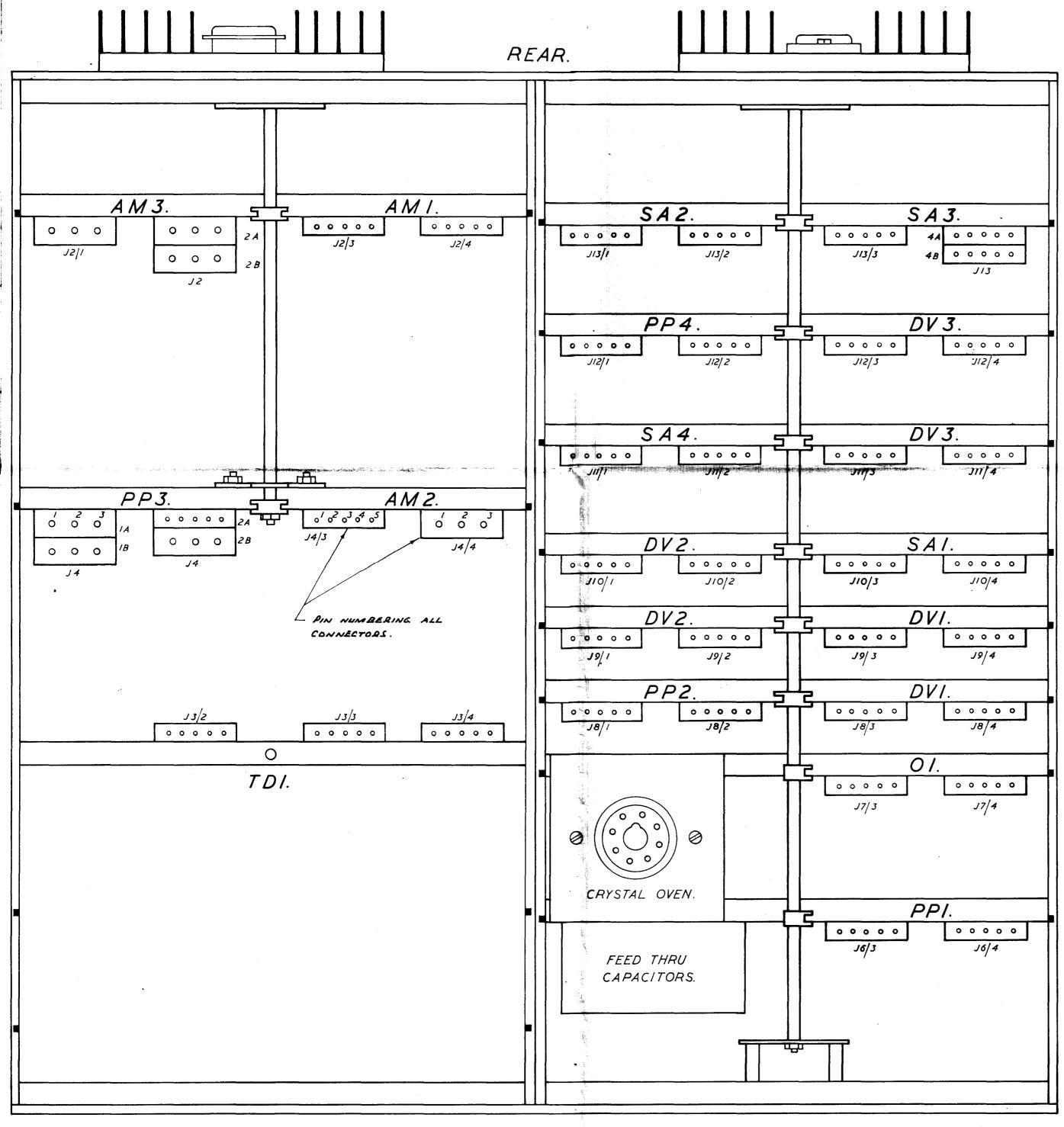

| Plate 22. Plan of card positions                     | (G82/3-122)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

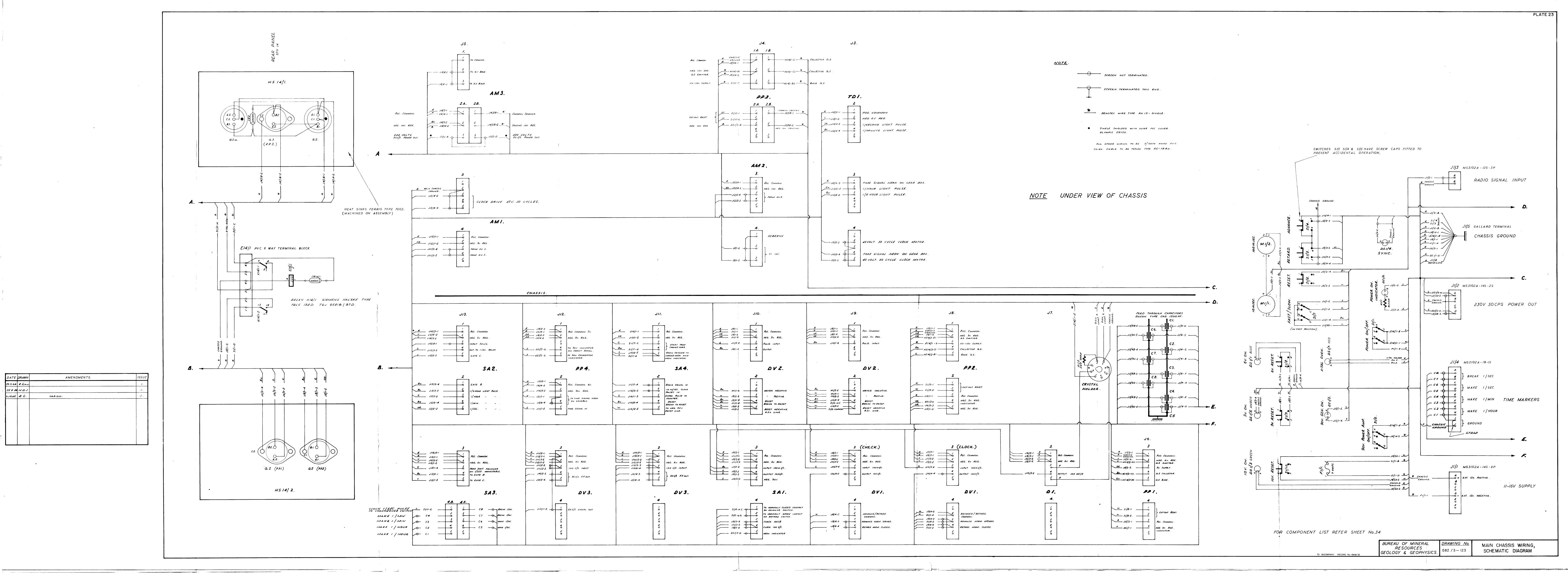

| Plate 23. Main chassis wiring, schematic diagram     | (G82/3-123)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

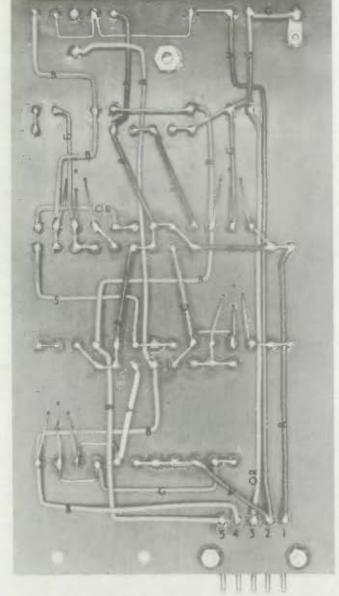

| Plate 24. Oscillator unit, component and wiring lay  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |