# DEPARTMENT OF NATIONAL RESOURCES NATIONAL DEVELOPMENT

## BUREAU OF MINERAL RESOURCES, GEOLOGY AND GEOPHYSICS

1979/66

065733

DEPARTMENT OF NATIONAL DEVELOPMENT

Bureau of Mineral Resources

Geology and Geophysics

Development of 8-channel digital-to-analogue conversion card for HP 2100 series computers

by

#### A.B. Devenish

The information contained in this report has been obtained by the Department of National Resources as part of the policy of the Australiam Government to assist in the exploration and development of all resources. It may not be published in any form or used in a company prospectus or statement in the permission in writing of the Director, Bureau of Mineral Resources, Geology and Geophysics.

BMR Record 1979/66 c.3

## 1979/66

#### DEPARTMENT OF NATIONAL DEVELOPMENT

Bureau of Mineral Resources

Geology and Geophysics

Development of 8-channel digital-to-analogue conversion card for HP 2100 series computers

bу

A.B. Devenish

### Contents

| 1 | In | tr | od | nc | ti | on   |

|---|----|----|----|----|----|------|

| • | -  |    |    |    | _  | ~ 44 |

- 2. Functional Description

- 3. Circuit Description

- 4. Specifications

- 5. Testing

- 6. Usage

- 7. Schematics, Artwork and parts list

Sheet 1 Schematic

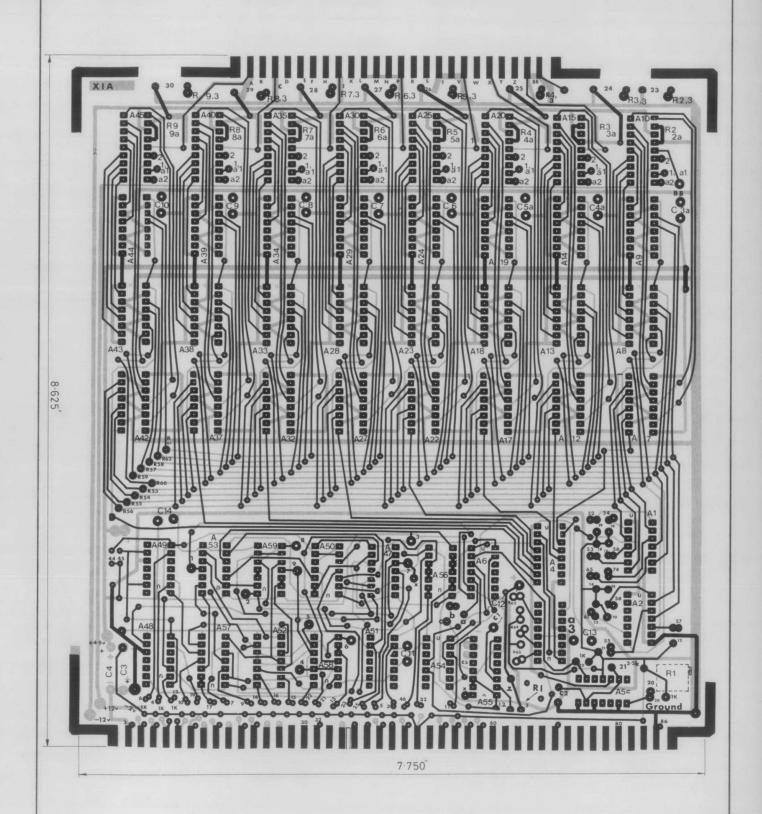

Sheet 1 (iv) Artwork

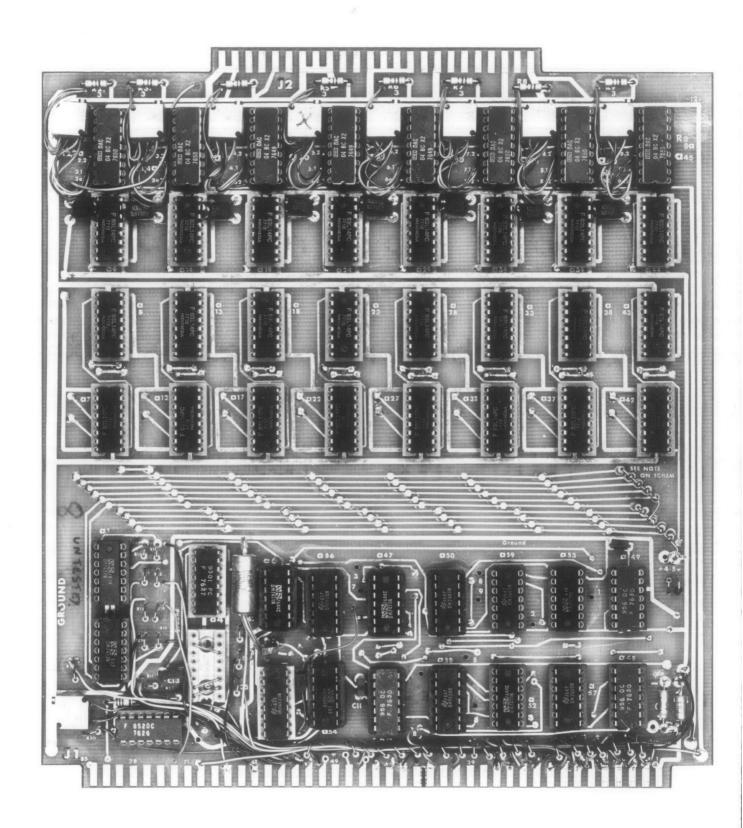

Sheet 1 ( v) Photograph of card

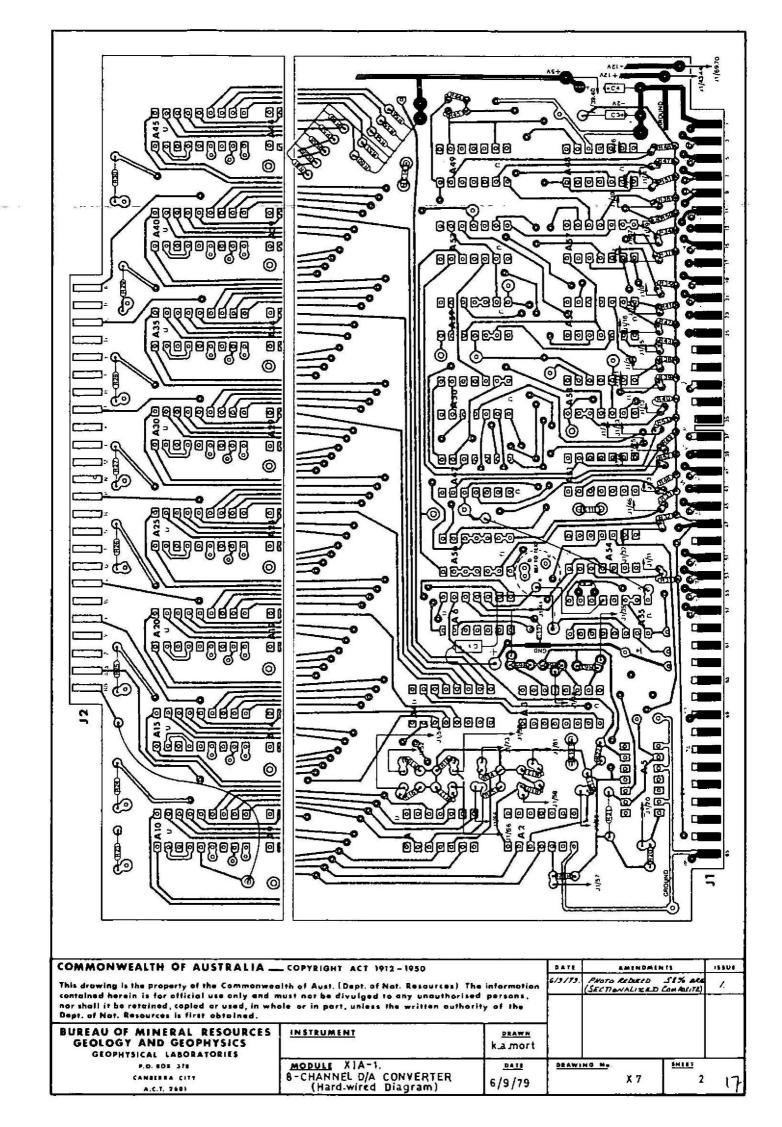

Sheet 2 (X7) Hard wired diagram

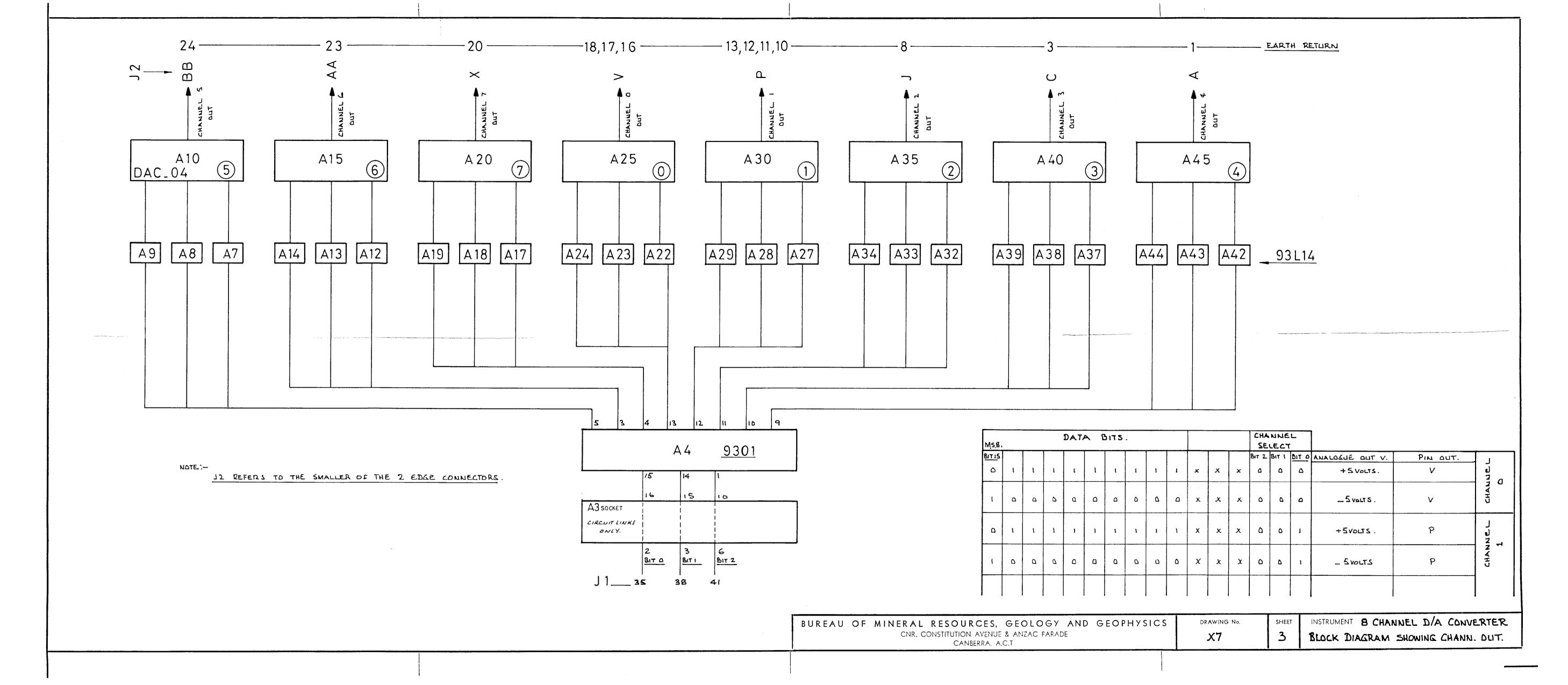

Sheet 3 Block diagram

Sheet 4 (i) & 4 (ii) Parts List

## Tables and Figures

| Figure   | <u>Title</u>               | Page |

|----------|----------------------------|------|

| Fig. 3.1 | Block Diagram              | 2    |

| Fig. 3.2 | 9301 Truth Table           | 3    |

| Fig. 3.3 | Latch Pulse and Data Pulse | 4    |

|          | time relationship          |      |

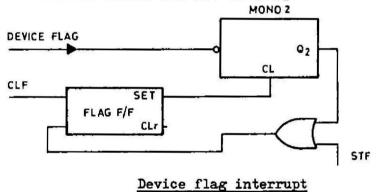

| Fig. 3.4 | Device flag interrupt      | . 5  |

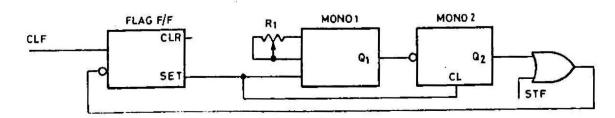

| Fig. 3.5 | Time delay interrupt       | 5    |

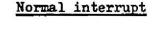

| Fig. 3.6 | Normal interrupt           | 6    |

| Fig. 3.7 | DAC-04 Input/Output Table  | 7    |

#### 1. Introduction

Hewlett Packard manufactures a two-channel digital-to-analogue conversion card for use in HP 2100 series computers. In BMR applications, however, the airborne system requires the monitoring of 7 quantities, the magnetotelluric system 5, and the marine system 4. For this reason, it was decided to develop an 8-channel digital-to-analogue (D/A) conversion card for use in HP 2100 computers.

An HP 12620A breadboard card was available for trying test circuits. First one channel was constructed and tested using CMOS logic; this logic type was found to be too slow to be used. Next a test circuit was constructed using TTL logic; this proved satisfactory. Low-power TTL was used in the production cards to reduce the amount of power used and heat produced. This was necessary since the final card contains 50 integrated circuits.

Three types of D/A chips made by Precision Monolithics Inc. were tested. They were the DAC 100, DAC 02, and DAC 04. The DAC 100 is a straight binary input, 0-10 volt output device. The DAC 02 is a sign magnitude input device with a -10 to +10 volt output. The DAC 04 is a 2's complement input device with a -5 to +5 volt output. One complete card was made using DAC 100 chips. This card worked correctly. However, BMR's marine group decided that they preferred a card using 2's complement D/A converters.

#### 2. Functional Description

The function of this card is to receive 13 data bits and 21 signal lines from the back plane of a HP 2100 computer. Three bits are used to determine which of the analogue outputs is selected. The other 10 bits contain the data to be converted to an analogue voltage. The data bits are in 2's complement form.

The flag, interrupt and control circuitry on the board is used for the control of interrupts. When the control flip-flop is set, the computer is ready to receive an interrupt and, when the flag flip-flop is set, an external device has requested an interrupt. This part of the circuitry was added to so it could function in three ways:

- (i) An external device can set the computer flag.

- (ii) The flag can be set at preset time after being cleared.

- (iii) Setting the flag causes the program to jump to the memory location equal to the select code of the card.

Choice of operating mode is determined by hand-wired links.

#### 3. Circuit Description

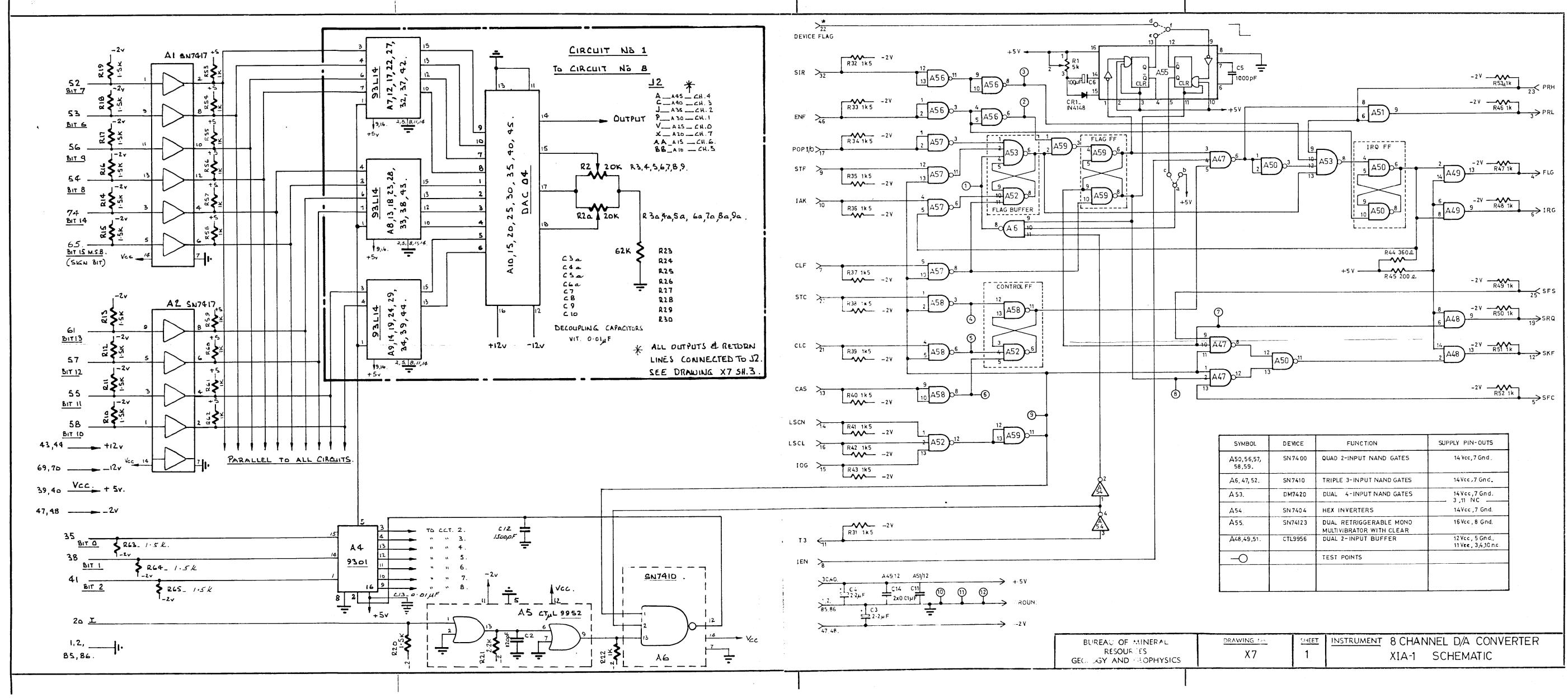

Block Diagram DATA DATA D/A BITS LATCH ANALOQUE OUTPUT TO OTHER CHANNELS DATA LATCH LINE OF 10 DECODER CHARRIEL 10 OTHER 13 SHILLER CHANNELS DITS SIGNALS WHICH ARE TRUE WHEN THE SELECT CODE OF THE CARD IS CHOSEN 1/0 OUTPUT PULSE

Fig. 3.1

The card receives 13 bits from the computer. Three of these are used to determine which of the eight D/A channels is to receive the ten data bits. This is achieved using a 1 of 10 decoder type 9301. The A, B and C inputs are used to determine which output line goes low and enables the data of a certain channel. The D latch input is used to disable the selection of one of the eight channels when it is not required. The truth table for the 9301 decoder is as follows:

|   | In | put | <u>8</u> |     |   |   |   | Out | put | 8 |   |   |   |

|---|----|-----|----------|-----|---|---|---|-----|-----|---|---|---|---|

| D | C  | В   | A        | 0   | 1 | 2 | 3 | 4   | 5   | 6 | 7 | 8 | 9 |

| 0 | 0  | 0   | 0        | 0   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 0 | 0  | 0   | 1        | 1   | 0 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 0 | 0  | 1   | 0        | 1   | 1 | 0 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 0 | 0  | 1   | 1        | 1   | 1 | 1 | 0 | 1   | 1   | 1 | 1 | 1 | 1 |

| 0 | 1  | 0   | 0        | . 1 | 1 | 1 | 1 | 0   | 1   | 1 | 1 | 1 | 1 |

| 0 | 1  | 0   | 1        | 1   | 1 | 1 | 1 | 1   | 0   | 1 | 1 | 1 | 1 |

| 0 | 1  | 1   | 0        | 1-  | 1 | 1 | 1 | 1   | 1   | 0 | 1 | 1 | 1 |

| 0 | 1  | 1   | 1 .      | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 0 | 1 | 1 |

| 1 | 0  | 0   | 0        | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 0 | 1 |

| 1 | 0  | 0   | 1        | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 0 |

| 1 | 0  | 1   | 0        | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 1 | 0  | 1   | 1 + .*   | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 1 | 1  | 0   | 0        | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 1 | 1  | 0   | 1        | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 1 | 1  | 1   | 0        | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

| 1 | 1  | 1   | 1        | 1   | 1 | 1 | 1 | 1   | 1   | 1 | 1 | 1 | 1 |

#### 9301 Truth Table

It can be seen from the truth table that when D is high none of the channels 0 to 7 can be low. Input D only goes low when the select code of the card is chosen and a OTA/B instruction is given e.g. OTA 11 when the card is in slot 11. This enables the card to ignore all the data on the lines except when an OTA/B instruction to the card's select code is executed.

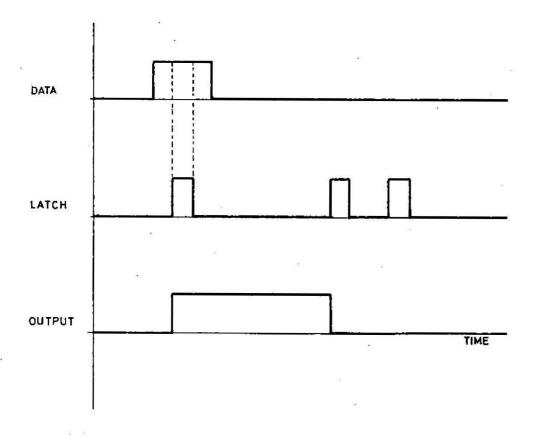

When the data latch line is low, the output of the data latch follows the input. When it goes high, the output is latched. The data and latch pulse time relationship is represented in the following diagram.

#### Latch Pulse and Data Pulse time relationship

Fig. 3.3

<sup>\*</sup>OTA/B - output the A or B register

The flag and interrupt circuitry is a copy of the standard Hewlett Packard flag and interrupt circuitry found on the Hewlett Packard breadboard card type 1260. A few extra components were added to enable the computer program to loop for an adjustable period. This was to allow time for pen movement if the card was used to drive a chart recorder. The magnetotelluric system required that the flag flip-flop could be set from an external device. Provision was made for this mode of operation.

A summary of the three ways the flag and interrupt circuitry can be used are as follows:

(a) An external device can set the flag on the card.

Fig. 3.4

An external device triggers mono 2 which toggles the flag flipflop. When set goes high, it clears mono 2. To be operated this way, the output from mono 1 is disconnected from mono 2 and the input of mono 2 is connected to the device flag.

(Links d - f and a - c connected)

(b) The flag is set at preset time after being cleared.

#### Time delay interrupt

The clear flag instruction (CLF) causes the set output of the flag flip-flop to go low. This triggers monostable 1 which causes Q1 to go high for a time adjustable by R1. When Q1 goes low again monostable, 2 is triggered which causes Q2 to go high. This in turn toggles the flag flip-flop which causes the set side to go high again which clears monostable 2.

(Links e - f and c - a connected).

(c) If the user doesn't wish to use either of the first two options, he can disable both of them by disconnecting the monostable from the flag flip-flop.

(Link a - b connected)

Fig. 3.6

#### 4. Specifications

- Physical Dimensions 196.8 mm x 220.7 mm

(Designed to fit into a HP 2100 computer mainframe).

- 2. Word format

Bits 0-2 for channel selection

Bits 15-6 for data input

- 3. Logic format

The DAC chips used are 2's complement devices. The following table shows output for given inputs.

## DAC 04 Input/Output Table

|   |     | <u>I</u> | npu | <u>t</u> |   |     |   |   |   | Output      |

|---|-----|----------|-----|----------|---|-----|---|---|---|-------------|

| Ō | . 1 | 1        | 1_  | 1_       | 1 | 1   | 1 | 1 | 1 | 5.000volt   |

| 0 | 1   | 1        | 1   | 1        | 1 | 1   | 1 | 1 | 0 | 4.990 volt  |

| 0 | 0   | 0        | 0   | 0        | 0 | 0   | 0 | 0 | 1 | 0.010 volt  |

| 0 | 0   | 0        | 0   | 0        | 0 | 0   | 0 | 0 | 0 | 0.000 volt  |

| 1 | 1   | 1        | 1   | 1        | 1 | . 1 | 1 | 1 | 1 | -0.010 volt |

| 1 | 0   | 0        | 0   | 0        | 0 | 0   | 0 | 1 | 0 | -4.990 volt |

| 1 | 0   | o        | 0   | 0        | Q | 0   | 0 | o | 1 | -5.000 volt |

4. Logic Type.

#### TTL and low power TTL

5. Interrupt, flag and control circuitry.

The board contains the logic circuitry of the HP 12620A breadboard card plus extra components to carry out the following functions:

- (i) Set the flag at preset time after being cleared.

- (ii) Set the flag from an external device.

#### 5. Testing

Various programs have been written to test the cards. The simplest being to output data from the switch register to the card. The code for it is as follows:

START

LIA 1

Load the A register from the switch register

OTA SC

Output the A register to the card

JMP

START Jump back to start.

This program enables the checking of DC voltages out for various data inputs for each channel.

Another program which outputs DC ramps for each channel is as follows:

|       | LDA             | x \  | Increment the A register by 1008 to                                    |

|-------|-----------------|------|------------------------------------------------------------------------|

| START | ADA             | x }  | Increment the A register by 1008 to increment the analogue output.     |

|       | CCB             | }    | Use the B register as channel select.                                  |

| LOOP  | INB             | )    | select.                                                                |

|       | CPB<br>·<br>JMP |      | Check for last channel  If last channel increment A  register by 1008. |

|       | IOR             | 1    | Form word with data and channel select                                 |

|       | OTA             | sc   | Output word to card.                                                   |

| a x   | AND :           | MASK | remove the channel select from the card.                               |

|       | JMP :           | LOOP |                                                                        |

MASK 177700<sub>8</sub>

Y 10<sub>8</sub>

X 100<sub>8</sub>

Part of the airborne software package includes a test of the 8 channel D/A card using a chart recorder.

Programs to test the three modes of operation of the flag and interrupt circuitry are as follows:

(a) The flag is set a preset time after being cleared. (e - f and c - a connected).

| START | CLF   | SC      | clear flag                      |

|-------|-------|---------|---------------------------------|

|       | SFS   | sc }    | wait for flag to be set         |

|       | JMP   | * - 1 } |                                 |

|       | INA   |         | Increment A                     |

|       | OTA 1 |         | Output A to the switch register |

|       | JMP   | START   |                                 |

Changing the monostable timing resistor changes times between counts as seen on the switch register.

(b) The flag is set by an external device. (d - f and c - a connected).

| START | CLF | SC      | clear flag                      |

|-------|-----|---------|---------------------------------|

| 14    | SFS | sc }    | wait for flag to be set         |

|       | JMP | * - 1 } | e e                             |

|       | INA |         | Increment A                     |

| ×     | OTA | 1 ,     | Output A to the switch register |

|       | JMР | START   |                                 |

Each time an external device flag is received, the A register and switch register imcrement.

(c) An internal interrupt causes the program to jump to the memory location of the cards select code. (a - b connected).

| START | STF, 0 | enable interrupt system         |

|-------|--------|---------------------------------|

|       | STF SC | interrupt                       |

|       | *      | 8                               |

| sc    | JMP    | GO                              |

|       |        |                                 |

| GO    | INA    | Increment A                     |

|       | OMA 4  | Outside the the suite marietan  |

|       | OTA 1  | Output A to the switch register |

|       | JMP GO |                                 |

The program is started at START and jumps to GO which can be seen by the counting of the switch register.

#### 6. Usage

The cards are used in computers in the airborne survey aircraft, magnetotelluric survey truck, marine data acquisition system and magnetogram digitiser. In the magnetotelluric system, it is used to monitor analogue outputs of the three magnetic channels and two electric channels recorded. In the airborne system, they produce analogue outputs of the four radiometric channels, altitude, magnetometer and Doppler navigation information.

#### COMMONWEALTH OF AUSTRALIA \_\_ COPYRIGHT ACT 1912-1950 DATE AMENDMENTS ISSUE 248/16 CARD REDUCED BY~11% This drawing is the property of the Commonwealth of Aust. (Dept. of Nat. Resources) The information contained herein is for official use only and must not be divulged to any unauthorised persons, nor shall it be retained, copied or used, in whole or in part, unless the written authority of the Dept. of Nat. Resources is first obtained. BUREAU OF MINERAL RESOURCES GEOLOGY AND GEOPHYSICS INSTRUMENT DRAWN R. GAN GEOPHYSICAL LABORATORIES SHEET DRAWING No. P.O. BOX 378 MODULE DATE CANBERRA CITY 1(v). 13 & CHANNEL DIA CONVERTER. 16-2-76 A.C.T. 2601

#### COMMONWEALTH OF AUSTRALIA \_\_ COPYRIGHT ACT 1912-1950 ISSUE This drawing is the property of the Commonwealth of Aust. (Dept. of Nat. Resources) The information contained herein is for official use only and must not be divulged to any unauthorised persons, nor shall it be retained, copied or used, in whole or in part, unless the written authority of the Dept. of Nat. Resources is first obtained. BUREAU OF MINERAL RESOURCES GEOLOGY AND GEOPHYSICS INSTRUMENT DRAWN 2. GAN GEOPHYSICAL LABORATORIES MODULE XIA- 1 P.O. BOX 378 DATE DRAWING No. SHEET SCHANNEL DIA CONVERTER. 16-2-76 X7 1 (iv). A.C.T. 2601

|                                                          |        |        |         | PARTS LIST                            |             |                |                    |              |

|----------------------------------------------------------|--------|--------|---------|---------------------------------------|-------------|----------------|--------------------|--------------|

| ITEM                                                     | VALUE  | W.v.   | Tol.    | TYPE                                  | MAKE        | MAKERS<br>REF. | BMR VOCAB          | QTY          |

| A1,2.                                                    |        |        |         | HEX. BUFFERS/DRIVERS                  | TEXAS INST. | SH7417N        | BUT-7417N          | 2.           |

| 14.                                                      |        |        | <u></u> | 4 INPUT. I OF 10 DECODER              | FAIRCHILD   | 9301           | BUS_689301         | /.           |

| A5.                                                      |        |        |         | DUAL 2-INPUT NOR GATE                 | <i>"</i>    | 9952 PC        | BUE_992 PC         | 1.           |

| A6, 47, 52.                                              | _      |        |         | TRIFLE 3-INPUT NAND GATES             | TEXAS INST. | SNTAION        | N.1.V.             | <b>.₹</b> .  |

| A7, 8,9,<br>12,13,14,<br>17,18,19                        |        |        |         |                                       |             |                |                    |              |

| 22, 23, 24,<br>27, 28, 29,<br>32, 33, 34,<br>37, 38, 39, | }      |        |         | 4BIT D. LATCHES                       | FAURCHILD   | 931 14PC       | BUS_ 931.14PC      | 24           |

| 42,43,44                                                 | }      |        |         |                                       |             |                |                    |              |

| AID, IS, 20.<br>25, 30, 35,<br>40, 45.                   |        |        |         | TNO'S COMPLEMENT 10 BIT DIA CONVERTER | P.M.I.      | DAC-04BCXZ     | BUZ-04BCX2         | 8.           |

| A48, 49,<br>51.                                          |        |        |         | DUAL Z-INPUT BUFFER                   | FAIRCHILD   | 9956 PC        | BUE_ 9956 PC       | _ <b>3</b> . |

| A50,56,<br>57,58,59.                                     |        |        |         | QUAD 2-INPUT NAND GATES               | TEXAS INST. | SN74-00N       | BUT_ 7400 N        | <i>5</i> .   |

| A53.                                                     |        |        |         | DUAL A-INPUT NAME GATES               | "           | SN7420N        | BUT_ 7420N         | 1.           |

| A54.                                                     |        |        | _       | HEX. INVERTERS                        | "           | SN 7404N       | BUT-7404 N         | 1.           |

| A55.                                                     |        |        |         | DUAL RT MONO MULTIVIBRATOR /CLA       | "           | SN74/23N       | N. 1. V.           | 1.           |

|                                                          |        | -      |         |                                       | ,, <u></u>  |                |                    | -            |

|                                                          |        |        |         |                                       |             |                |                    |              |

|                                                          | 72     | -      | _       |                                       |             |                |                    |              |

|                                                          |        |        | _       |                                       |             |                |                    |              |

|                                                          |        |        | _       |                                       |             |                |                    |              |

| <del></del>                                              | 1      |        | _       |                                       |             |                |                    |              |

|                                                          | _      | _      |         |                                       |             |                |                    |              |

|                                                          |        |        |         |                                       |             |                |                    |              |

|                                                          |        | -      |         |                                       |             |                |                    |              |

| BUDEAL                                                   | . 05 : | 415155 |         | RESOURCES INSTRUMENT:                 |             | СОМІ           | PONENTS : /. C. 'S | [            |

BUREAU OF MINERAL RESOURCES | INSTRUMENT: **GEOLOGY AND GEOPHYSICS** P.O. BOX 378, CANBERRA CITY, A.C.T. 2601

8 CHANNEL DIA CONVERTER.

SHEET Nº: △63

ISSUE

MODULE:

DATE 21/8/79.15

X/A-1

|                                 |         |       |      | PARTS LIST                  | Γ        |                            |                |     |

|---------------------------------|---------|-------|------|-----------------------------|----------|----------------------------|----------------|-----|

| ITEM                            | VALUE   | W.v.  | Tol. | TYPE                        | MAKE     | MAKERS<br>REF.             | BMR VOCAB      | QTY |

| C6                              | 10005   | IOV   | 20   | SOLID TANTALUM CAPACITOR.   | KEMET    | TIIOC-<br>IOTK-<br>OOIOAS. | BCK_02/07      | 1.  |

| CZ.                             | 120005  | 1001  | 10   | CAPACITOR, CERAMIC, CK.     | VITRAMON | CKOSBX-<br>122K.           | BCA_ 1122      | 1.  |

| <i>C3,4</i> .                   | 2.2,45  | 20 V  |      | CAPACITOR, SOLID TANTALUM.  | KEMET    | THOA -<br>225K-<br>020AS.  | BCK_03225      | 2.  |

| C30, 60,<br>50,60,<br>7-11, 14. | אענסים  | 100 v | 10   | CAPACITOR, CERAMIC, CK.     | YITKAMON | LX05BX-<br>103K            | BCA- 1103      | 10. |

| <i>L13</i> .                    | 1500pF  | IDOV  | 10   | CAPACITOR, CERAMIC, CK.     | *        | CK05BX-<br>152K            | BCA_ 115Z      | 1.  |

| <i>L5</i> .                     | 1000 pF | 200   | 10   | CAPACITOR, CERAMIC, CK.     | <i>u</i> | IOZK                       | BCA_ 210 2     | 1.  |

|                                 |         |       |      |                             |          |                            |                |     |

| RI.                             | 5Ks     |       |      | 1/2 H TRIMPOT, 25TURN.      | Bourns   | 3282L                      | BPC_3502       | 1.  |

| Rz_9,<br>Kla_9a.                | 20KSL   |       |      | 1/2 TRIMPOT 25 TURN         | "        | 3282L                      | BPC_3203       | 16. |

| RIO_ 19,<br>32-43,<br>43-45,    | 1:5Ka   | 0.1 W | 2    | RESISTER, METAL FILM, MK25. | PHILIPS  | 2372-151-<br>4150Z         | BRA_55152      | 25  |

| R21.                            | 2.2Ks   |       | "    | RESISTOR, METAL FILM, MR25. |          | 1322-/5/-<br>42202         | BRA-55222      | 1.  |

| R 22,53a,<br>46_52,<br>53_62.   | IKD     | *     | ,,   | RESISTOR, METAL FAM. MRZS.  | u        | 2122-151-<br>41002         | BRA_55102      | 19. |

| R2330.                          | 62KA    | "     | .,   | RESISTOR, METAL FILM, MR25. | <i>"</i> | 2322-151-<br>46203.        | BRA_55623      | 8.  |

| RAA.                            | 3601    | "     |      | RESISTOR, METAL FILM, MRZS. | -        | 2322-/S/-<br>4360/         | BRA-55361      | 1.  |

| R45.                            | 2000    | •     | -    | RESISTOR, METAL FILM, MR25. | <u>"</u> | 2322-151-<br>42001         | BRA_55201      | 1.  |

| 4.00                            |         |       |      |                             |          |                            |                |     |

|                                 |         |       |      |                             |          |                            |                | -   |

|                                 |         |       | _    |                             |          |                            |                |     |

|                                 |         |       | _    |                             |          |                            |                |     |

|                                 |         |       |      |                             |          |                            |                |     |

|                                 |         |       |      |                             |          |                            |                |     |

|                                 |         | L     |      |                             |          | Took                       | PONENTS: Pas a |     |

BUREAU OF MINERAL RESOURCES

GEOLOGY AND GEOPHYSICS

P.O. BOX 378, CANBERRA CITY, A.C.T. 2601

INSTRUMENT:

8CHANNEL DIA CONVERTER.

COMPONENTS: RESE CAPS.

SHEET Nº: 4(ii)

MODULE: DI

XIA-1

DATE 21/8/79.

| DRAWN    | DATE    | C'K'D | AMENDMENTS                                    | ISSUE |

|----------|---------|-------|-----------------------------------------------|-------|

| Q. LAN   | 12/8/17 |       |                                               | /     |

| K.A.MORT | 17/8/79 |       | IC A3 DELETED SOCKET NOWUSED AS CIRCUIT LINK. | 2     |

|          |         |       |                                               |       |

|          |         |       |                                               |       |

|          |         |       |                                               |       |

|          |         |       |                                               |       |

|          |         |       |                                               |       |

## COMMONWEALTH OF AUSTRALIA

## COPYRIGHT ACT 1912-1950

THIS DRAWING IS THE PROPERTY OF THE COMMONWEALTH OF AUSTRALIA (DEPARTMENT OF NATIONAL DEVELOPMENT).

THE INFORMATION CONTAINED HEREIN IS FOR OFFICIAL USE ONLY AND MUST NOT BE DIVULGED TO ANY UNAUTHORISED PERSONS, NOR SHALL IT BE RETAINED, COPIED OR USED, IN WHOLE OR IN PART, UNLESS THE WRITTEN AUTHORITY OF THE DEPARTMENT OF NATIONAL DEVELOPMENT IS FIRST OBTAINED.

| DRAWN  | DATE     | C'K'D | AMENDMENTS                           | ISSUE |

|--------|----------|-------|--------------------------------------|-------|

| R. GAN | 18-2-76  |       |                                      | _ /   |

| R.GAN  | 23.3.76  |       | VARIOUS                              | 2     |

| KAMORT | 17/8/179 |       | GATING CIRCUITRY REDRAWN, DELETE A3. |       |

## COMMONWEALTH OF AUSTRALIA

#### COPYRIGHT ACT 1912-1950

THIS DRAWING IS THE PROPERTY OF THE COMMONWEALTH OF AUSTRALIA (DEPARTMENT OF NATIONAL DEVELOPMENT).

THE INFORMATION CONTAINED HEREIN IS FOR OFFICIAL USE ONLY AND MUST NOT BE DIVULGED TO ANY UNAUTHORISED PERSONS, NOR SHALL IT BE RETAINED, COPIED OR USED, IN WHOLE OR IN PART, UNLESS THE WRITTEN AUTHORITY OF THE DEPARTMENT OF NATIONAL DEVELOPMENT IS FIRST OBTAINED.

## NOTE:-

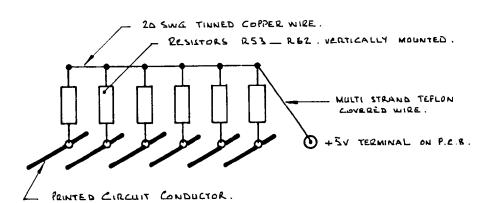

MOUNTING PROCEDURE FOR RESISTORS 253 \_ R62.