1983/8

Ø3

BMIR PUBLICATIONS COMPACTUS

(LENDING SECTION)

105331 105991

# BUREAU OF MINERAL RESOURCES, GEOLOGY AND GEOPHYSICS

RECORD

RECORD No. 1983/8

MAGNETOTELLURIC SIGNAL AMPLIFICATION AND FILTERING - A NOVEL CIRCUIT DESIGN

by

Y.S.B. LIU

The information contained in this report has been obtained by the Bureau of Mineral Resources, Geology and Geophysics as part of the policy of the Australian Government to assist in the exploration and development of mineral resources. It may not be published in any form or used in a company prospectus or statement without the permission in writing of the Director.

# RECORD No. 1983/8

MAGNETOTELLURIC SIGNAL AMPLIFICATION AND FILTERING - A NOVEL CIRCUIT DESIGN

by

Y.S.B. LIU

# CONTENTS

| 1.   | Intro | duction                                                |     |

|------|-------|--------------------------------------------------------|-----|

| 2.   | Post  | - amplifier design considerations                      |     |

|      | 2.1.  | Problems at subaudio frequencies                       |     |

|      | 2.2.  | Thin film resistor network                             |     |

|      | 2.3.  | Application of the R - 2R network to sub-audio filters |     |

|      | 2.4.  | Filter realisation                                     |     |

| 3.   | Techn | ical description                                       |     |

| 1 20 | 3.1.  | Application                                            |     |

|      | 3.2.  | Block schematic description                            |     |

|      | 3.3.  | High pass filter                                       |     |

|      | 3.4.  | Low pass filter                                        |     |

|      | 3.5.  | Gain amplifier                                         | 1   |

| 4.   | 0pera | tion                                                   | 1   |

|      | 4.1.  | Inspection                                             | 1   |

|      | 4.2.  | Panel switch settings                                  | . 1 |

|      | 4.3.  | Channel positions                                      | 1   |

|      | 4.4.  | Power switch                                           | 1   |

|      | 4.5.  | Gain checking                                          | -1  |

|      | 4.6.  | Filter checking                                        | 1   |

| 5.   | Field | maintenance                                            | 1:  |

|      | 5.1.  | General precautions                                    | 1:  |

|      | 5.2.  | Trouble shooting of gain                               | 1:  |

|      | 5.3.  | Trouble shooting of HP filter                          | 1:  |

|      | 5.4.  | Trouble shooting of LP filter                          | 1   |

| App  | endix | A Specification summary                                | . 1 |

| App  | endix | B Transfer functions and pole-zero tabulations         | 2   |

| Dra  | wings |                                                        |     |

| м 2  | SH2a  | Magnetotelluric post-amplifier part A                  |     |

M 2 SH2b Magnetotelluric post-amplifier part B

#### ABSTRACT

This Record describes a magnetotelluric postamplifier and filter operating from 0.001 - 40 Hz. A novel design approach utilises a binary weighted thin film resistor network to simulate accurately the very high resistances required for subaudio frequency applications. Other advantages for this approach include a minimum component count, active on-chip switching to avoid leakage and pick - up, and programmability by computer or master channel.

Field operation and maintenance procedures are included to enable this record to be used as a field operation manual.

#### 1. Introduction

The magnetotelluric (MT) method determines the impedance tensor derived from three magnetic induction components and two electric field components resulting from the interaction of electromagnetic fields with the conducting earth.

Induction coils, buried underground for thermal stability and wind noise reduction, sense the variations in magnetic induction. Over the conventional MT frequency spectrum of almost five decades (0.0006 Hz to 40 Hz) these variations reduce rapidly in amplitude with increasing frequency. The resulting dynamic range exceeds 100 dB for measurements over the full spectrum; the maximum resolution required is about one microtesla.

Signals from the induction coils are amplified by the so-called H preamplifiers in the front end of the modified Geotronics system operated by BMR. In the original analogue sample, the H preamplifier outputs were further amplified and filtered in post-amplifiers with manually operated gain and filter settings. For BMR's digital data acquisition, however, new post-amplifiers were designed to permit gain and passband selection either by the system computer or manually, with the switch settings encoded for acquisition with the data. In the new design, variable high-pass and low-pass active RC filters divide the frequency spectrum into seven overlapping passbands. The dynamic range needed for measurement in any one passband is less then the wideband dynamic range because of the frequency dependence of magnetic induction amplitudes.

#### 2. Post - amplifier design considerations

#### 2.1. Problems at sub-audio frequencies

At the lowest MT frequencies RC filter time constants are of the order of hundreds of seconds. The necessarily high capacitance values limit the types and, therefore, the characteristics of capacitors which can be used. Polystyrene and polypropylene capacitors, usually found in precision audio filters because of their low losses and low temperature coefficients, are physically too large to be manufactured with high capacitance values. Precision polycarbonate capacitors have lower performance characteristics but are commercially available with values up to 22 µF. Resistances of up

to 12 megohm are then required to form time constants corresponding to 3 dB roll-off frequencies down to 0.0006 Hz.

Metal film resistors, because of their stability, are commonly used in filter applications and are available with low temperature coefficients (down to ± 10 ppm / °C). They are unsuitable for this sub-audio application, however, because generally available resistance values do not exceed 1 megohm. Resistor types, such as carbon film, metal oxide film and tin oxide film, are available in high resistances, but are not fully satisfactory because of low stability, high temperature coefficient, high cost or poor availability. In any case, the use of discrete resistors having values much above 1 megohm is inadvisable in field equipment; condensation from a humid atmosphere, particularly in dusty conditions, can form a significant and variable conducting path across the resistor.

Further practical problems arise from the need to switch time constants to give seven passbands each comprising a fourth-order low-pass and a second-order highpass filtering function - a total of six time constants to be switched. Each time constant is set by a precision capacitor and a resistance which is made up from a fixed preferred-value resistor and a trimming potentiometer. If the capacitors are switched the penalty is high cost and a very large circuit board to accommodate all the capacitors. Switching the resistors results in less troublesome switching transients, requires far less board space and is cheaper, so is generally preferred.

All the foregoing problems are eliminated by the use of thin-film resistor networks.

#### 2.2. Thin film resistor networks

Significant progress has been made over the past few years in thin film resistor technology. High-precision low cost thin film networks have become available in commercial quantities. The most commonly used thin film resistor materials are nichrome, tantalum and various cermets. They are deposited on alumina, ceramic or glass substrates. Advances in laser technology make it possible for low cost laser trimming of the resistance networks in automatic batch processing.

Besides providing savings in space and cost over assemblies of precision resistors, the thin film resistor network possesses excellent tracking properties of resistance-temperature coefficient. Typical coefficients are  $\pm$  20 to  $\pm$ 100 ppm/ $^{\circ}$ c but elements can track to within lppm/ $^{\circ}$ c

on the same substrates. The element resistance tolerance is within  $\frac{1}{2}$  20%, but the matching of absolute resistance between elements is better than 0.1%. Thus these elements are better utilised when providing resistance ratios, rather than as a group of independent resistors.

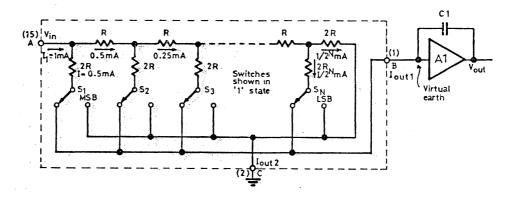

## 2.3. Application of the R-2R network to sub-audio filters

Thin film resistor networks have been widely used in programmable gain amplifiers and programmable filters. One network type, not normally associated with these applications, is the R-2R ladder (Figure 1) which is frequently used in digital to analogue converters (DAC). The binary weighted current division which occurs in this network allows very high effective resistances to be obtained from the moderate resistances of the R-2R structure. This is a very useful network configuration to realize sub-audio filters at 0.001Hz or below, where very high resistance elements with high stability and accuracy are required.

Fig. 1 Ladder Network with external amplifier and capacitor to form an integrator

Figure 1 shows an n-section R-2R ladder network with switches  $S_1$  to  $S_n$ . Common values for n in commercial DACS are 10 or 12, as in Analog

Devices types AD7530 and AD7541 which have CMOS integrated active switches. An Amplifier A1 and a capacitor C1 are connected to one of the outputs to form an integrator. The binary weighted currents are switched between the I and I out 2 terminals, depending on the logic input states to the switches S1 to Sn. With digital switch control inputs low, current is switched to I out 2, otherwise to I out 1. Because Terminal B (I out 1) is connected to the virtual earth of integrator amplifier A1 the input resistance looking into terminal A is always R, i.e. 10K ohm in the case of the AD7530. However, the effective resistance from Terminal A to Terminal B depends on the amount of current shunted by the switches. Assuming Sn only is closed, i.e. in the '!' state, the current into the virtual earth is

I out 1 (n) =

$$\frac{1}{2^n}$$

(1)

In general, for any switch state

$$I_{out 1} = MI_{1}$$

(2)

where

$$M = \sum_{i=1}^{n} A_{i}$$

$$i = 1 \frac{1}{2^{i}}$$

(3)

$A_{i}$  may be 0 or 1 depending on the control signal to the i th switch.

Thus the transresistance from Terminal A to Terminal B is

$$R_{AB} = \frac{Vin}{MI_1}$$

$$= \frac{R}{M}$$

$$I_1 = \frac{Vin}{R}$$

(4)

since

For a 10-bit device with R = 10K,  $R_{AB}$  has 1023 values in the range 10.01k ( $A_i$  = 1 for all i) to 10.24 M ( $A_i$  = 1 for i = 10 only).

Similarly for a 12 - bit device there are 4095 values between 10.002 k and 40.96 M.

Thus the output voltage from the integrator circuit of Figure 1 is

$$Vo (s) = Vin (s) s C_1 (R/M)$$

(5)

The following section shows how this circuit is used in the programmable filter.

Programmable gain is obtained by connecting the R-2R ladder network in the feedback path of an operational amplifier which has an input resistance R. The gain is

$$\frac{\text{Vo}}{\text{Vin}} = \frac{R_{AB}}{R}$$

$$= \frac{1}{M}$$

(6)

#### 2.4. Filter realization

The state variable realization of a second order transfer function uses a three-amplifier double-integrator feedback loop to generate a transfer function having two complex conjugate poles. The transfer functions describing the lowpass (LP) and highpass (HP) filters are:

$$T (LP) = \frac{H_e \omega_o^2}{s^2 + (\omega_o/Q)s + \omega_o^2}$$

(7)

$$T (HP) = \frac{H_h s^2}{s^2 + (\omega_Q/Q)s + \omega_Q^2}$$

(8)

Where H is the gain constant, s is the complex frequency variable,  $w_0/2\pi$  is the natural frequency and 1/20 is the damping factor.

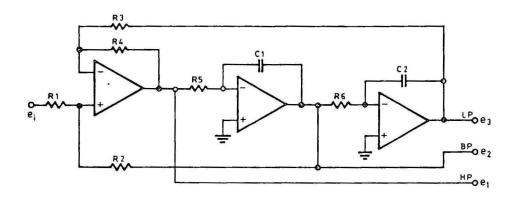

Fig. 2. State variable realization of LP, HP and BP filters.

For the three amplifier realization of Figure 2 it can be shown that

$$\omega_{0} = \sqrt{\frac{R4}{R3R5R6C1C2}}$$

(9)

$$Q = \frac{(R1+R2)}{R1(R3+R4)} = \frac{R3R4R5C1}{R6 C2}$$

(10)

By equating R2 = R3 = R4 then

$$\omega_{o} = \frac{1}{\sqrt{R5R6C1C2}} \tag{11}$$

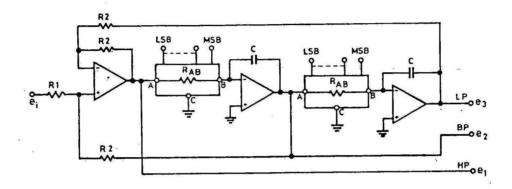

$\,$  If R5 and R6 are replaced with the R-2R ladder network, then Figure 2 can be redrawn as in Figure 3.

Figure 3. State variable filter incorporating R-2R ladder network.

In this case, R5 = R6 =

$$R_{AB}$$

and  $C1$  =  $C2$  =  $C$

then equation (11) becomes

$$\omega_{O} = \frac{M}{R.C} \tag{12}$$

Where M is as defined in equation (3). Therefore one can realise a very large range of cut off frequencies by

simply changing the logic inputs to the ladder network.

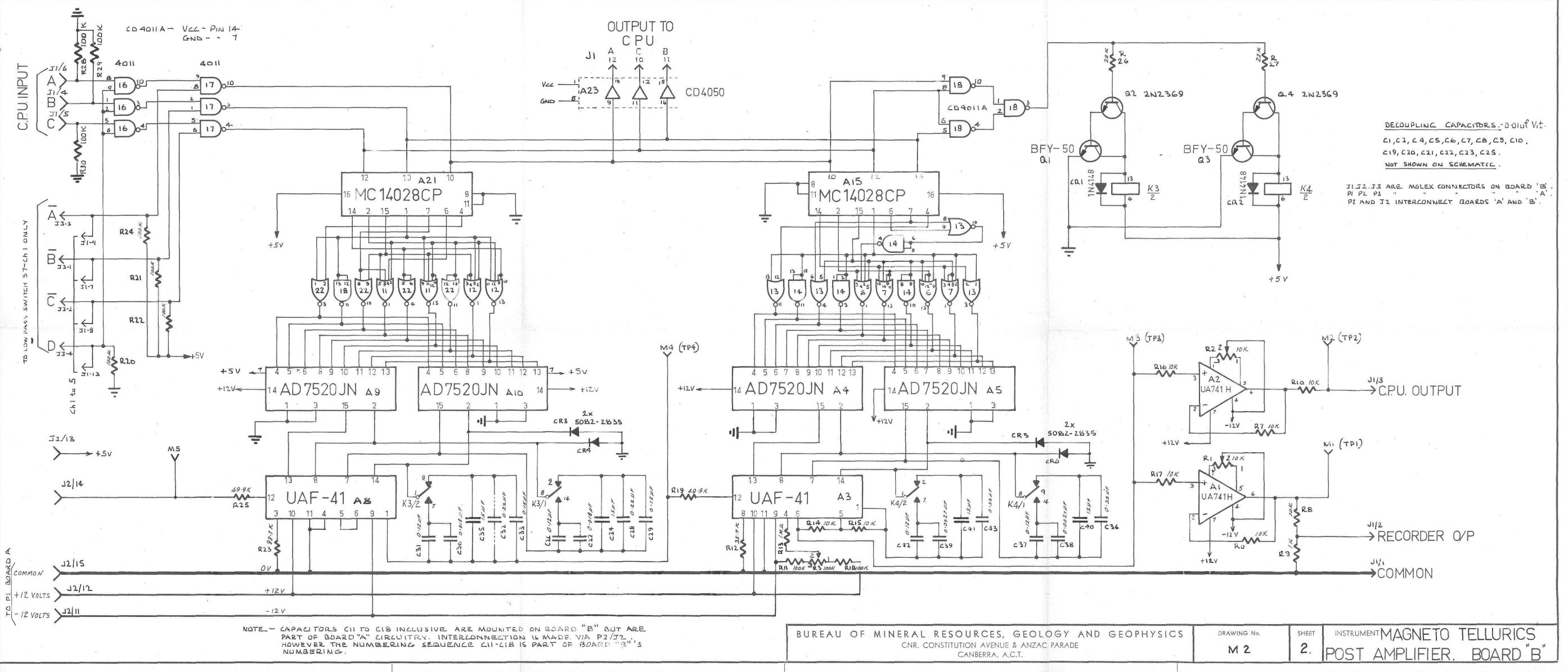

#### 3. Technical Description

# 3.1. Application

The MTA-1 Post Amplifier is designed for use in the Magnetotelluric system. It accepts outputs from the H and E preamplifiers, performs bandwidth shaping and amplification, then interfaces the analogue signals to the computer and monitoring device. Gain settings on all five channels are independent of each other, but they can be controlled by the computer. The filter settings can either be slaved to channel 1, or be programmed by the computer. Logic codes of all five channels of filter and gain settings are sent to the Digital Multiplexer for data logging.

#### 3.2. Block Schematic Descriptions

The Post Amplifier consists of four basic functional blocks from input to output: a low noise front end with a gain of 30, a two-pole Butterworth high-pass filter, and a post amplification gain of 100 followed by a four-pole Bessel low-pass filter. Two separate buffered outputs are provided: a unity gain buffer to the A/D converter and a 1/10 buffer to the recorder output terminal. All gain and filter settings are controlled either by the front panel switches or by the coded logic from the computer.

Physically the amplifier consists of two printed circuit boards. The amplifiers (maximum gain of 3000) and high-pass filter are located in Board A, whereas the low-pass filter and output buffers are located in Board B. To minimise the spacing between the two boards, all the switching capacitors associated with the high pass filter are actually located in Board B via the Utilux connector  $P_2$ .

To minimize 50-Hz pick up, a separate stand-alone power supply delivers  $\pm$  15 V to the post amplifier. Within each amplifier channel there are two separate regulators: a  $\pm$  12V tracking regulator for the analogue circuitry, and a +5V regulator for the digital logic. Both regulators are located in Board A.

The only interconnections between the five channels are the power supply rails and the eight logic switching wires, four for the high-pass and four for the low-pass filters.

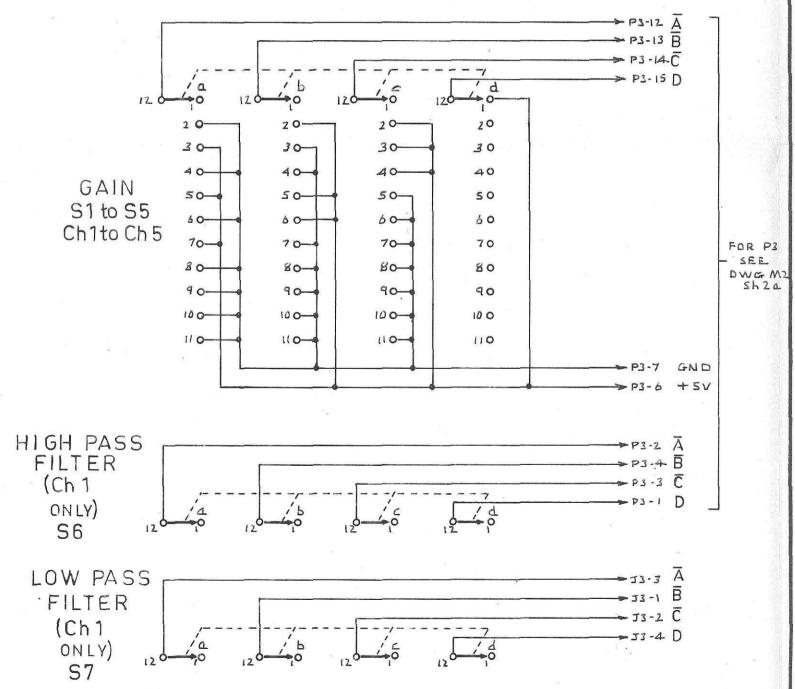

#### 3.3. High-pass filter

- (a) The high-pass filter consists of amplifier A13a, A13b and A13c forming a 3 amplifier double integrator loop, with  $A_{12}$  and  $A_{11}$  binary ladder networks used as resistor  $R_{AB}$ . The basic circuit connection is the same as that shown in Figure 3.  $A_{10}$ ,  $A_{1}$ ,  $A_{20}$  and  $A_{21}$  are associated with logic decoding to select the weighted binary network elements for various frequency ranges.

- (b) Two sets of capacitors located in Board B are associated with the high-pass filter. Positions 1-4 are associated with one set of capacitors with a nominal value of 31 uF, whereas positions 5-7 are associated with another group of capacitors with a nominal value of 0.5 uF. The switching of capacitors is accomplished by a two-pole change-over relay. A push button is provided in the front panel (HP By-Pass) to discharge the 31 uF capacitors via a two-pole relay and 100 ohm resistors, hence reducing the

settling time at lower cut-off frequencies.

(c) A21 and A22 are slaved to channel I for range switching:

| POSITION | LOGIC<br>A B C | 3 dB FREQUENCY Hz |

|----------|----------------|-------------------|

| 1        | 100            | 0.001             |

| . 2      | 0 1 0          | 0.01              |

| 3        | 1 1 0          | 0.03              |

| 4        | 0 0 1          | 0.1               |

| 5        | 101            | 0.5               |

| 6        | 0 1 1          | 2.5               |

| 7        | 1 1 1          | 10                |

NOTE: Logic 1 is at +5V and logic 0 at ground potential.

#### 3.4. Low-pass filter

- (a) The low-pass filter consists of two cascaded two-pole Bessel filters. Two sets of capacitors are associated with each section of the filter. The switching of capacitors is by two-pole changeover relays. In both sections, positions 1-4 share one set of capacitors, and positions 5-7 share the other set.

- (b)  $A_8$ ,  $A_9$ ,  $A_{10}$  form the first two pole filter;  $A_3$ ,  $A_4$ ,  $A_5$  form the second.  $A_{21}$  and  $A_{15}$ , with associated gates, form logic decoders to select the weighted binary network elements for various frequency ranges.

- (c) A<sub>16</sub>, A<sub>17</sub> and A<sub>18</sub> are slaved to channel 1 for range switching:

| POSITION |   | LOGIC<br>A B C | 3 dB FREQUENCY Hz |

|----------|---|----------------|-------------------|

|          |   |                |                   |

| 1        |   | 1 0 0          | 0.012             |

| 2        |   | 0 1 0          | 0.033             |

| 3        |   | 1 1 0          | 0.12              |

| 4        |   | 0 0 1          | 0.55              |

| 5        | * | 1 0 1          | 2.5               |

| 6        |   | 0 1 1          | 12.5              |

| 7        |   | 1 1 1          | 40                |

# 3.5. Gain Amplifier

- (a) The gain is distributed between two stages: the first stage (A23) has a maximum gain of 30 and the second stage (A24) a maximum gain of 100. Al4 and Al5 are the weighted binary networks forming the input and feedback resistors for the amplifiers. A9, AlO and the associated gates form the logic decoder to select the binary network elements.

- (b) The dynamic range of the power spectral density is about 140-160 dB in the frequency range of 0.001-40 Hz, with signals decreasing rapidly at the higher frequencies. The present arrangement of gain in relation to the filter positions is the result of compromise between dynamic range and other important performance characteristics like noise, drift etc.

(c) A25, A26 and A28 are slaved to channel I for gain range switching:

| Position |   |   | OGI<br>B | В | lst Stage<br>Gain | 2nd Stage<br>Gain | Total<br>Gain |

|----------|---|---|----------|---|-------------------|-------------------|---------------|

| 1        |   | 1 | 0        | 0 | 1                 | 3                 | 3             |

| 2        | , | 0 | 1        | 0 | 2                 | 5                 | 10            |

| 3        |   | l | 1        | 0 | 2                 | 15                | 30            |

| 4        |   | 0 | 0        | 1 | 2                 | 50                | 100           |

| 5        |   | 1 | 0        | 1 | 3                 | 100               | 300           |

| 6        |   | 0 | 1        | 1 | 10                | 100               | 1000          |

| 7        |   | 1 | 1        | 1 | 30                | 100               | 3000          |

#### 4. Operation

#### 4.1. Inspection

Upon arrival at the survey location, visual inspection should be carried out on all electro-mechanical aspects of the unit, including inteconnection cables, chassis wiring and components mounted within each amplifier module. Care should be exercised to avoid rubbing printed circuit board interconnection wiring when removing the top panels from the module for component inspection. On replacing the modules into the bin, all five channels should be fastened with mounting screws.

#### 4.2. Panel Switch Settings

To avoid excessive switching transients and prolonged filter settling time, it is good practice to have the filters at moderate frequency settings, say 40 Hz for LP and 0.1 Hz for HP, and the gain setting at 3, prior to switching the power on or off.

Neither the gain nor the filter switches should be left in the CPU position, as there are no CPU switching input facilities in the present operating system.

#### 4.3. Channel Positions

The chassis is wired such that Channel I amplifier should always be placed in the leftmost slot. Channels 2-5 can be placed in the remaining slots in random order. However it is recommended that they should be placed in an orderly sequence from Channel I for ease of identification. The SPARE channel can be placed either in Channel I slot or in Channel 2-5 slots. When it is in Channel I slot, its filter and gain settings can be in any position except CPU or SLAVE, but if it is in any of Channel 2-5 slots, its filter switches must be left in the SLAVE position; the gain switches can be in any position except CPU.

#### 4.4. Power Switch

It is good practice to switch on the stand-alone  $\pm$  power supply before switching on the post amplifier power supply. Power should be switched off when inserting or withdrawing the amplifier modules from the bin.

#### 4.5. Gain Checking

A functional gain check should be carried out at least once a week or on arrival at a new survey location.

Set LP filters at 40Hz and HP filters at 0.1 Hz. Apply 1Hz signal from the calibration unit to the post amplifiers. Check the seven gain settings on each of the five amplifier channels. Visual observation of the amplifier outputs on the strip chart recorder or CRO should be sufficient for this purpose.

Any excessive noise or feed-through should be investigated.

#### 4.6. Filter Checking

A functional filter check should be carried out at least once a week or on arrival of a new survey location.

- (a) Set LP filter at 40Hz and HP filter at 0.03 Hz. Set gain of amplifier at 3. Set calibrator frequency at 1Hz and then 0.03 Hz, and observe the outputs of all five channels at the recorder. The output levels at 0.03 Hz should be 70% of those at 1 Hz.

- (b) Set HP filter at 0.1 Hz with the settings of LP filter and gain unchanged. Set calibrator frequency at 1 Hz and then 0.1 Hz, and observe the outputs of all five channels at the recorder. The output levels at 0.1 Hz should be 70% of those at 1 Hz.

- (c) Set HP filter at 0.01 Hz with gain at 3. Set LP filter at 0.55 Hz. Set calibrator frequency at 0.1 Hz and then 0.55 Hz. Allow sufficient time for the amplifier to settle down in each case and observe the outputs of all five channels at the recorder. The output levels at 0.55 Hz should be 70% of those at 0.1 Hz.

- (d) Set HP filter at 0.001 Hz with gain at 3. Set LP filter at 0.12 Hz. Set calibrator frequency at 0.02 Hz and then 0.12 Hz. Allow at least 30 minutes for the amplifier to settle down in each case and observe the outputs of all five channels at the recorder. The output levels at 0.12 Hz should be 70% of those at 0.02 Hz.

#### 5. Field maintenance

#### 5.1. General Precautions

- (a), The calibration and alignment of the Post Amplifier is generally a precise and tedious process requiring precision instruments in a laboratory environment. Field maintenance therefore should be restricted to the minimum possible.

- (b) Two types of integrated circuits are used in the unit: linear analogue amplifiers, and CMOS for logic and D/A convertors. The use of an ohmmeter or DVM to measure continuity of circuitry should therefore be avoided unless the revelant ICs are unplugged or the amplifier modules are withdrawn from the bin when checking the chassis wiring.

- (c) To carry out trouble shooting in a particular amplifier channel, the use of an extension lead is convenient. If an extension lead is unavailable, the suspected channel, with four module panels withdrawn, can be plugged into location 3 or 4, with the adjacent channels withdrawn from

the bin. In this way both PCBs of the suspected channel are accessible to the CRO probe.

In general it should be possible to replace an IC without separating the PCB from the module. Particular care is necessary to ensure correct orientation of the ICs.

(d) It is not recommended to dismantle the printed circuit boards from the modules in the field. If this becomes absolutely necessary, the easiest way is to unplug the Utilux connectors J1 and J2 in Board B, and unsolder four wires at J3 (note the colour code). This is followed by unscrewing the two screws in each of the front and rear subpanels which secure the module rails of Board B. Then Board B with its module rails can be lifted up from the module. In re-assembling the module, the reverse process is applied. Take particular care to inspect the Utilux connectors, adjusting the spring contacts if necessary.

# 5.2. Trouble shooting of Gain

If the gain in a particular channel appears suspect, the following steps can be adopted:

- (a) Ascertain the fault is not caused by malfunction of HP or LP filters by checking the filter's frequency response with the calibrator. Check power supply rails and ensure there is no output saturation.

- (b). Check the logic codes of the gain switch positions either on the teleprinter or by direct measurement at the CPU output connector of the post amplifier. If any channel gives output gain logic of 000 (undefined), check +5V supply of that channel. If the output gain logic disagrees with the switch positions, check A25-28 on Board A according to the logic truth table. Replace any IC found faulty.

- (c) If no fault could be found with step (b), use the CRO to monitor M2 and M4 of Board A to decide which section of the amplifier is faulty. Check outputs of A9 or A18 with the truth table below:

| Position      |    |   | PIN NO | OF N | 1C 14028 | (A | 9 <b>,</b> A(18) |  |

|---------------|----|---|--------|------|----------|----|------------------|--|

|               | 14 | 2 | 15     | 1    | 6        | 7  | 4                |  |

| 1 (gain 3)    | 1  | 0 | 0      | 0    | 0        | 0  | 0                |  |

| 2             | 0  | 1 | 0      | 0    | 0        | 0  | 0                |  |

| 3             | 0  | 0 | 1      | 0    | 0        | 0  | 0                |  |

| 4             | 0  | 0 | 0      | ì    | 0        | 0  | 0                |  |

| 5             | 0  | 0 | 0      | 0    | 1        | 0  | 0                |  |

| 6             | 0  | 0 | 0      | 0    | 0        | 1  | 0                |  |

| 7 (gain 3000) | 0  | 0 | 0      | 0    | 0        | 0  | 1                |  |

Replace IC A9 or A18 if found faulty.

(d) If no fault could be found with step (c), check inputs of Al4 and Al5 with the truth tables below:

| Position      |   | PI | NO N | OF AD | 7530 | (A14) |    |    |    |    |     |

|---------------|---|----|------|-------|------|-------|----|----|----|----|-----|

|               | 4 | 5  | 6    | 7     | 8    | 9     | 10 | 11 | 12 | 13 |     |

| (gain 3)      | 1 | 1  | 1    | 1     | 1    | 1     | 1  | ì  | 1  | 1  |     |

| . 2           | 1 | 0  | 0    | 0     | 0    | 0     | 1  | 0  | 0  | 0  |     |

| 3             | 1 | 0  | 0    | 0     | 0    | 0     | 0  | 0  | 0  | 0  | ,÷j |

| 4             | 1 | 0  | 0    | 0     | 0    | 0     | 1  | 0  | 0  | 0  | (3  |

| 5             | 0 | 1  | 0    | 1     | 0    | 1 .   | 1  | 1  | 0  | 0  |     |

| 6             | 0 | 0  | 0    | 1     | i    | 0     | 1  | 0  | 0  | 0  |     |

| 7 (gain 3000) | 0 | 0  | 0    | 0     | 1    | 0     | 0  | 0  | 1  | 1  |     |

| Position      |   | PI | NO N | OF AD | 7530 | (A15) |    |    |    |    |     |

| *             | 4 | 5  | 6    | 7     | 8    | 9     | 10 | 11 | 12 | 13 |     |

| 1 (gain 3)    | 0 | 1  | 0    | 1     | 0    | 1     | 0  | ı  | 0  | 1  | -   |

| 2             | 0 | 0  | 1    | - 1   | 0    | 0     | 1  | 0  | 0  | 0  |     |

| 3             | 0 | 0  | 0    | 1     | 0    | 0     | 0  | 1  | 0  | 0  |     |

| 4             | 0 | 0  | 0    | 0     | 0    | 1     | 0  | 1  | 0  | 0  |     |

| 5             | 0 | 0  | 0    | 0     | 0    | 0     | 1  | 0  | 1  | 0  |     |

| 6             | 0 | 0  | 0    | 0     | 0    | 0     | 1  | 0  | 1  | 0  |     |

| 7 (gain 3000) | 0 | 0  | 0    | 0     | 0    | 0     | 1  | 0  | 1  | 0  |     |

If either of these truth tables cannot be met, trace the trouble to A5-8 and A16-17, replace any IC found faulty.

- (e) If no fault could be found with step (d) replace A!4 or A!5 as required.

- (f) If the fault is still not rectified after steps (b) to (e), replace IC A23 or A24 as required.

- (g) If the fault is still not rectified after steps (b) (f), the gain stages are most likely not faulty. One should look for the fault elsewhere.

#### 5.3. Trouble shooting of HP Filter

If the HP filter in a particular channel appears suspect, the following steps can be adopted:

- (a) Ascertain the fault is not caused by malfunction of gain or LP filter by checking the amplifier frequency and gain response with the calibrator. Check + 12V and +5V power supply. Check that there is no output saturation. All circuitry of HP filter is in Board A, but its capacitors are located in Board B.

- (b) Check logic codes of HP switch positions by direct measurement. If any channel gives output HP logic of 000 (undefined), check +5V supply of that channel. If the output HP filter logic disagrees with the switch positions, check A21 and A22 on Board A according to the logic truth table. Replace any IC found faulty.

- (c) If no fault could be found with step (b) check outputs of AlO with the truth table in 5.2 (c). Position I in this case corresponds to 0.001 Hz HP filter setting. Replace IC AlO if found faulty.

- (d) If no fault could be found with step (c). Check inputs of All and Al2 with the truth table below:

| Position     |   | P | IN | NO | OF | AD7 | 530 | (A]] | , A l | 2) |  |

|--------------|---|---|----|----|----|-----|-----|------|-------|----|--|

|              | 4 | 5 | 6  | 7  | 8  | 9   | 10  | 11   | 12    | 13 |  |

| 1 (0.001 Hz) | 1 | i | 1  | 1  | 1  | 1   | 1   | 1    | 0     | 1  |  |

| 2            | ì | 1 | 1  | 1  | 1  | 0   | 1   | 0    | 1     | 1  |  |

| . 3          | 1 | 1 | 1  | 1  | 0  | 0   | 0   | 0    | 1     | 1  |  |

| 4            | ì | l | 0  | 0  | 1  | 1   | 0   | 1    | 1     | i  |  |

| 5            | 1 | 1 | 1  | 1  | 1  | 0   | 1   | 1    | 1     | 1  |  |

| 6            | 1 | 1 | 1  | 0  | 1  | 0   | 1   | 1    | 1     | 1  |  |

If conditions of this truth table cannot be met, trace the trouble to Al, 20, 21. Replace any IC found faulty.

1010111111

7 (10 Hz)

- (e) If no fault can be found with step (d), determine which range of HP filter is not working. If position 1-4 is not working but position 5-7 is working (or vice versa), then check changeover operation of relay K1.

- (f) If no fault could be found with steps (a)-(e) replace All or Al2 as required. This is a step to be avoided if possible. In any event, the method and precautions outlined below should be strickly observed.

- (i) Use a fully floating DVM to measure resistance between Pin 16 and Pin 1 of the IC AD7530, with the positive terminal of DVM to Pin 1 and the common terminal of DVM to pin 16.

- (ii) Using the same method choose a replacement IC with the same resistance between pin 1 and pin 16.

- (iii) Record this replacement (Channel No, and IC no. and resistance of IC) in the dairy. This should be reported to the laboratory project officer on return from the survey, so that response of this channel can be checked and recalibrated if necessary.

- (g) IC Al3 is a home-made IC replacing the Burr-Brown UAF41. Inspect this IC assembly referring to the UAF41 data sheet and repair if necessary. As a functional test only, one can temporarily replace the homemade IC with a Burr Brown UAF 41. The output noise and offset would increase with UAF41. This step would indicate whether the home-made IC is faulty.

#### 5.4. Trouble shooting of LP Filter

If the LP filter is a particular channel appears suspect, the following steps can be adopted:

- (a) Ascertain the fault is not caused by malfunction of gain or HP filter by checking the output of board A at test point M2. All circuitry of LP filter is located in Board B.

- (b) The four-pole LP Bessel filter is composed of two cascaded two-pole LP filters. Test point M4 is the output of the first section, and test point M3 is the output of the second section. Both sections share the same switching decoding logic. One should try to isolate the trouble to the first section (M4) or second section (M3), or the switching logic itself. Check + 12V and +5V power supplies.

- (c) Check logic codes of LP switch positions by direct measurement, If any channel gives output LP logic of 000 (undefined), check +5V supply of that channel. If the output LP filter logic disagrees with the switch positions, check A16 and A17 on Board B according to the logic truth table. Replace any IC found faulty.

- (d) Check output of A15 and A21 with the truth table in 5.2 (c). Position 1 in this case corresponds to 0.012 Hz LP filter setting. Replace IC A15 or A21 if found faulty.

- (e) Check inputs of A9, A10 or A4, A5 with the truth tables below:

Position PIN NO OF AD7530 (A9, A10)

| 1 (0.012 Hz) 1 1 1 1 1 | 3 9 10 11 12 13 |

|------------------------|-----------------|

|                        |                 |

| 2 1 1 1 1 0            | 1 0 1 1 1 0     |

| 2 1 1 1 0              | 0 1 0 0 0 0     |

| 3 1 0 1 0              | 0 1 0 1 0 1     |

| 4 0 0 1 1 1            | 1 1 0 1 0 0     |

| 5 . 1 1 1 1 0          |                 |

| 6 1 1 0 1 0            |                 |

| 7 (40 Hz) 0 1 1 1 1    |                 |

| Position     |   | P | IN | NO | OF | AD7 | 530 | (A4, | A5) |    |

|--------------|---|---|----|----|----|-----|-----|------|-----|----|

|              | 4 | 5 | 6  | 7  | 8  | 9   | 10  | 11   | 12  | 13 |

| 1 (0.012 Hz) | 1 | 1 | 1  | ì  | 1  | 0   | 1   | 1    | 0   | 0  |

| 2            | ì | 1 | 1  | 1  | 0  | 0   | 1   | 0    | 1   | 1  |

| 3            | 1 | 1 | 0  | ì  | 0  | 0   | 0   | 0    | 0   | 1  |

| 4            | 0 | 0 | 1  | 0  | 0  | 1   | 1   | 0    | 0   | 0  |

| 5            | 1 | 1 | 1  | 1  | 0  | 1   | 1   | 1    | 1   | 1  |

| 6            | 1 | 1 | 0  | 1  | 0  | 1   | 1   | 1    | 1   | 1  |

| 7 (40 Hz)    | 0 | 1 | 1  | 1  | 1  | 1   | 1   | 1    | 1   | 1  |

If either of these truth tables cannot be met, trace the trouble to All, Al2, Al8, A22 or A6, A7, Al3, Al4. Replace any IC found faulty.

- (f) If no fault could be found with steps (a) (e), replace A9 or A10, A4 or A5 as required. This is a step to be avoided if possible. In any event, the method and precautions outlined in step 5.3 (f) should be strictly observed.

- (g) Check IC A8, A3 A1, A2. Replace any IC found faulty.

#### APPENDIX A

Specification Summary

Number of Channels: five

Gain Steps: 3, 10, 30, 100, 300, 1000, 3000

High Pass Filter (3 dB points): 0.001, 0.01, 0.03, 0.1, 0.5, 2.5, 10 Hz.

Low Pass Filter (3 dB points): 0.012, 0.033, 0.12, 0.55, 2.5, 12.5, 40 Hz.

Noise: luV r.m.s. rti 0.001-40 Hz

Output voltage: + 12V on cpu output terminal

+ 1.2V on Recorder output terminal

Input impedance: 10 kohm

External Power Requirement: + 15 V 400 mA maximum.

Internal Power Supply: + 12V, + 5V

Physical Dimension: Case 221.5 mm height x 483 mm width x 477 mm depth

Operating temperature: 0-50°C

Connectors: Input - BNC floating

Output - BNC single ended

Power - Cannon 14-P-5P

A - + 15V

B - - 15V

C - OV

# APPENDIX B

(1) Transfer function for low pass filter:

$$T(LP) = \frac{81.00175}{s^2 + 17.24388 f_c^s + 81.00175 f_s^s} \cdot \frac{101.81655}{s^2 + 12.52628 f_s^s + 101.81655 f_c^s}$$

Complex poles tabulation (s in Hz):

| Freq | uency    |          |          | <u>.</u> | Comp       | lex poles |

|------|----------|----------|----------|----------|------------|-----------|

| 0.01 | 2 Hz     |          |          | -0.01647 | <u>+</u> j | 4.934 E-3 |

|      |          |          |          | -0.01196 | <u>+</u> j | 0.01511   |

|      |          |          |          |          |            |           |

| 0.03 | 3 Hz     |          |          | -0.04528 | <u>+</u> j | 0.01356   |

|      |          |          |          | -0.0329  | <u>+</u> j | 0.04156   |

|      |          |          |          |          |            |           |

| 0.12 | Hz       |          |          | -0.1647  | <u>+</u> j | 0.04934   |

|      |          |          |          | -0.1196  | <u>+</u> j | 0.1511    |

|      |          |          |          |          |            |           |

| 0.55 | Hz       |          |          | -0.7547  | <u>+</u> j | 0.2258    |

|      |          |          |          | -0.5483  | <u>+</u> j | 0.69248   |

|      |          |          |          |          |            |           |

| 2.5. | Hz       |          |          | -3.4298  | <u>+</u> j | 1.0270    |

|      | •        |          |          | -2.4924  | <u>+</u> j | 3.1481    |

|      | *        |          |          |          |            |           |

| 12.5 | Hz       |          |          | -17.157  | <u>+</u> j | 5.1359    |

|      |          |          |          | -12.46   | <u>+</u> j | 15.739    |

|      |          |          |          |          |            |           |

| 40 H | Z        |          |          | -54.893  |            |           |

|      |          |          |          | -39.868  | <u>+</u> j | 50.365    |

| (2)  | Transfer | function | for high | pass fil | ter:       |           |

|      | m(up) -  |          |          | s 2      |            |           |

$$T(HP) = \frac{s^2}{s^2 + 8.88572 f_c s + 39.47842 f_c s}$$

Complex poles tabulation (s in Hz):

0.001 Hz

0.01 Hz

-0.03 Hz

-0.1 Hz

0.5 Hz

2.5 Hz

10 Hz

# Complex poles

-7.071E-4 + j 7.071E-4

-7.071E-3 + j 7.071E-3

-2.1214E-2+ j 2.1214E-2

-7.071E-2 + j 7.071E-2

-0.3536 + j 0.3536

-1.7678 <u>+</u> j 1.7678

-7.071 + j 7.071

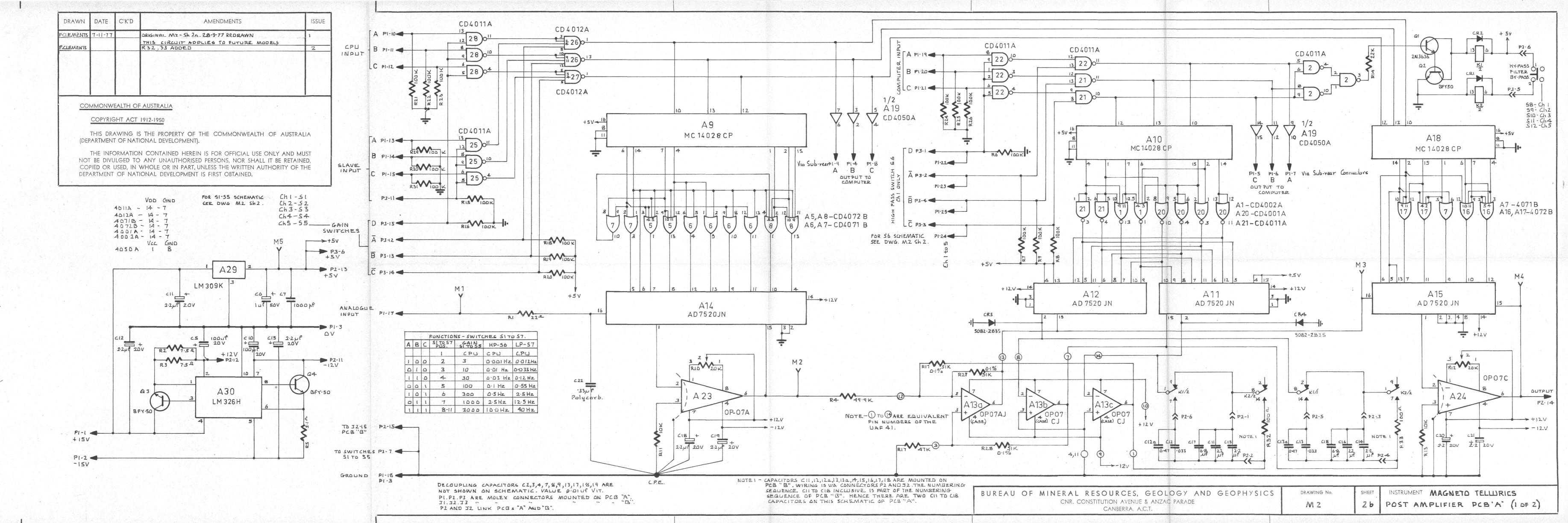

| DRAWN      | DATE     | C'K'D | AMENDMENTS                                         | ISSUE |

|------------|----------|-------|----------------------------------------------------|-------|

| K.A.M      | 12/4/77  |       | PROTOTYPE                                          | /     |

| F.LLEMENTS | 27.9.77  |       | R28.29.30 ADDED. A16.17.21.23.15418 CONFORM TO PCB | Σ     |

| F.CLEMENTS | 4-10-77  |       | VARIOUS MINOR                                      | 3     |

| F.CLEMENTS | 1 -10-77 |       | A 56.7.8. ADDED. VARIOUS MINUR.                    | 4     |

| FCLEMENT   | 85-11-77 |       | SWITCH SCHEMATICE SITO ST TRANSFERRED FROM Sh Za   | 5     |

| FLLEMENTS  | 20-6-78  |       | VARIDUS MINDR.                                     | 6     |

| F.CLEMENTS | 25-2-80  |       | Q5-Q8 REPLACED BY CR3-CR6                          | 7     |

# COMMONWEALTH OF AUSTRALIA

# COPYRIGHT ACT 1912-1950

THIS DRAWING IS THE PROPERTY OF THE COMMONWEALTH OF AUSTRALIA (DEPARTMENT OF NATIONAL DEVELOPMENT).

THE INFORMATION CONTAINED HEREIN IS FOR OFFICIAL USE ONLY AND MUST NOT BE DIVULGED TO ANY UNAUTHORISED PERSONS, NOR SHALL IT BE RETAINED, COPIED OR USED, IN WHOLE OR IN PART, UNLESS THE WRITTEN AUTHORITY OF THE DEPARTMENT OF NATIONAL DEVELOPMENT IS FIRST OBTAINED.